© 2012 IEEE

IEEE Transactions on Industrial Electronics, Vol. 59, No. 7, July 2012.

#### Efficiency-Optimized High-Current Dual Active Bridge Converter for Automotive Applications

F. Krismer J. W. Kolar

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of ETH Zurich's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

## Efficiency-Optimized High-Current Dual Active Bridge Converter for Automotive Applications

Florian Krismer, Student Member, IEEE, and Johann W. Kolar, Fellow, IEEE

Abstract—An efficiency-optimized modulation scheme and design method are developed for an existing hardware prototype of a bidirectional dual active bridge (DAB) dc/dc converter. The DAB being considered is used for an automotive application and is made up of a high-voltage port with port voltage  $V_1$ ,  $240~{

m V} \le V_1 \le 450~{

m V}$ , and a low-voltage port with port voltage  $V_2$ ,  $11 \text{ V} \leq V_2 \leq 16 \text{ V}$ ; the rated output power is 2 kW. A much increased converter efficiency is achieved with the methods detailed in this paper: The average efficiency, calculated for different voltages  $V_1$  and  $V_2$ , different power levels, and both directions of power transfer, rises from 89.6% (conventional phase shift modulation) to 93.5% (proposed modulation scheme). Measured efficiency values, obtained from the DAB hardware prototype, are used to verify the theoretical results.

Index Terms—Battery chargers, circuit optimization, dc-dc power conversion, design methodology, digital systems.

#### MOMENCE ARTICLE

|                                                   | Nomenclature                                        |  |

|---------------------------------------------------|-----------------------------------------------------|--|

| $D_1$                                             | Duty cycle used for the HV full bridge.             |  |

| $D_2$                                             | Duty cycle used for the LV full bridge.             |  |

| $\varphi$                                         | Phase angle between $v_{\rm T1}$ and $v_{\rm T2}$ . |  |

| $f_{ m S}$                                        | Switching frequency.                                |  |

| $i_{\mathrm{T1}}$                                 | Transformer current, HV side.                       |  |

| $i_{\mathrm{T2}}$                                 | Transformer current, LV side.                       |  |

| $I_{\rm S1,sw,min}$                               | Minimum HV MOSFET current needed to                 |  |

|                                                   | achieve low switching losses, HV side.              |  |

| $I_{ m S2,sw,opt}$                                | LV MOSFET current needed to achieve mini-           |  |

|                                                   | mum switching losses on the LV side.                |  |

| L                                                 | DAB converter inductance.                           |  |

| n                                                 | Transformer turns ratio.                            |  |

| $P_1$                                             | HV port power.                                      |  |

| $P_2$                                             | LV port power.                                      |  |

| $P_{ m out}$                                      | Converter output power.                             |  |

| $P_{ m out,d}$                                    | Designated output power (mod. scheme).              |  |

| $P_{\triangle,\mathrm{a,max}}$                    | Maximum power of the modified triangular            |  |

|                                                   | current mode modulation for $V_2 \leq V_{2,\lim}$ . |  |

| $P_{\triangle,\mathrm{b,max}}$                    | Maximum power of the modified triangular            |  |

|                                                   | current mode modulation for $V_2 \geq V_{2,\lim}$ . |  |

| $P_{\triangle, \text{V2} \text{lim}, \text{max}}$ | Maximum power of the modified triangular            |  |

|                                                   | current mode modulation at $V_2 = V_{2,lim}$ .      |  |

| $P_{\text{opt,a,min}}$                            | Minimum power of the high-power mod.                |  |

Manuscript received December 20, 2009; revised June 16, 2010 and October 6, 2010; accepted January 24, 2011. Date of publication February 7, 2011; date of current version February 17, 2012.

scheme for  $V_2 \leq V_{2,\text{lim}}(P_{\text{opt,a,min}} > P_{\triangle,\text{a,max}})$ .

The authors are with the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH) Zurich, 8092 Zurich, Switzerland (e-mail: krismer@lem.ee.ethz.ch; kolar@lem.ee.ethz.ch).

Digital Object Identifier 10.1109/TIE.2011.2112312

| $P_{\rm opt,b,min}$  | Minimum power of the high-power                                               |

|----------------------|-------------------------------------------------------------------------------|

|                      | mod. scheme for $V_2 \ge V_{2,\text{lim}}(P_{\text{opt,b,min}} >$             |

|                      | $P_{\triangle,\mathrm{b,max}}).$                                              |

| $P_{ m opt,a,hi}$    | Transition power level with $D_1 = D_2 = 0.5$                                 |

|                      | for $V_2 \leq V_{2,\text{lim}}(P_{\text{opt,a,hi}} > P_{\text{opt,a,min}})$ . |

| $P_{\max}$           | Maximum output power of the DAB.                                              |

| $T_{ m S}$           | Switching period, $T_{\rm S} = 1/f_{\rm S}$ .                                 |

| $V_1$                | HV port voltage.                                                              |

| $V_2$                | LV port voltage.                                                              |

| $V_{2,\mathrm{lim}}$ | Defines the boundary between different operat-                                |

|                      | ing modes of the DAB.                                                         |

| $v_{\mathrm{T1}}$    | AC volt. generated by the HV full bridge.                                     |

| $v_{\mathrm{T2}}$    | AC volt. generated by the LV full bridge.                                     |

#### I. INTRODUCTION

ECENT trends in the automotive industry toward electric vehicles, hybrid electric vehicles, and fuel-cell-powered vehicles create the need for highly compact, lightweight, and efficient power converters [1], to exchange electrical power between the various on-board power sources [2]. In order to further push existing limits, a procedure for efficiency-optimized converter design and modulation scheme are presented for a bidirectional automotive dc/dc converter. The dc/dc converter investigated here transfers power between the high-voltage (HV) dc port of a fuel cell stack and the dc port of a low-voltage (LV) battery [3], [4]. The converter specifications are:

- HV port: 240 V  $\leq V_1 \leq 450$  V, nominal voltage: 340 V;

- LV port: 11 V  $\leq V_2 \leq$  16 V, nominal voltage: 12 V.

The rated output power of the dc/dc converter considered here is 2 kW within the above specified voltage ranges and bidirectional converter operation. A high converter efficiency of more than 90%, high reliability, and high power density are required with respect to the application in a car [5]; moreover, the HV dc port must be isolated galvanically from the LV dc

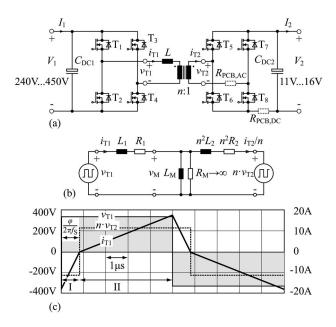

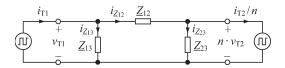

Typical topology candidates with these specifications include half- and full-bridge topologies with one or more dc inductors [6]–[8], the dual active bridge (DAB) converter [9]–[11], and resonant converter topologies [12]. Fig. 1(a) depicts the DAB converter, which is selected for the given application due to its soft-switching properties and the low number of passive components [13], making a highly compact converter feasible [7].

The conventional modulation scheme employed for the DAB converter [9], the so-called phase shift modulation, only achieves high converter efficiency for operating voltages close to  $V_1 \approx nV_2$  (Section V-C). For  $V_1 \ll nV_2$  or  $V_1 \gg$  $nV_2$ , the transformer rms currents, the inductor and transformer copper losses, and the semiconductor conduction losses

Fig. 1. (a) DAB topology; the resistors  $R_{\rm PCB,AC}$  and  $R_{\rm PCB,DC}$  model the printed circuit board (PCB) conduction losses; (b) employed electrical DAB model, which considers conduction losses and magnetizing current [11], [13]; and (c) calculated voltage and current waveforms for phase shift modulation,  $V_1=340~{\rm V}, V_2=12~{\rm V}, P_2=2~{\rm kW}, L=26.7~{\rm \mu H}, n=19.$

increase considerably [14]. Fig. 1(c) depicts typical current and voltage waveforms for phase shift modulation. The respective duty cycles  $D_1$  and  $D_2$  (defined in Fig. 3) are  $D_1=0.5$  and  $D_2=0.5$  for phase shift modulation.

Considerably increased converter efficiency can be achieved for a given DAB converter with the use of alternative modulation schemes, which use  $D_1 \leq 0.5$  and/or  $D_2 \leq 0.5$ . This paper aims to find a modulation scheme which enables converter operation at (or close to) maximum converter efficiency.

Initial investigations on alternative modulation schemes are given in [15] for a bidirectional ac/dc converter: The proposed alternative modulation schemes extend the zero-voltage switching (ZVS) range of the DAB and reduce the transformer rms currents (the principle of operation of ZVS is discussed in [16]). Detailed investigations of the modulation schemes presented in [15] with either  $D_1 \leq 0.5 \land D_2 = 0.5$  or  $D_1 = 0.5 \land D_2 \leq 0.5$  are presented in [17], [18]. The 1-D optimization problem (either  $D_1$  or  $D_2$  changes) with respect to maximal converter efficiency is solved in [17].

Highly efficient operation of the DAB is also achieved with modulation schemes employing  $D_1 \leq 0.5$  and  $D_2 \leq 0.5$  [19]–[22]. However, compared to the aforementioned 1-D problem, it is more complex to solve the resulting 2-D problem with respect to maximal efficiency [23]. Therefore, a more intuitive method is typically used to determine  $D_1$  and  $D_2$ , e.g., in [19], [21], where triangular or trapezoidal transformer currents are generated in order to achieve low switching and low conduction losses. Further efficiency improvements are reported with the use of a combination of different existing modulation schemes [24], [25].

This paper presents a systematic approach to derive an efficiency-optimized modulation scheme for the DAB, which enables ZVS on the HV side without the need for additional circuitry [26] and goes on to propose an efficiency-optimized selection of the transformer turns ratio n and the converter

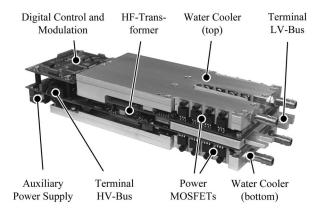

Fig. 2. 2-kW automotive DAB converter (273 mm  $\times$  90 mm  $\times$  53 mm); rated voltage transfer ratio:  $V_1=340$  V,  $V_2=12$  V.

inductance L used. Section II outlines the working principles of the DAB converter and Section III summarizes the converter loss model employed. Section IV details the results of the numerical search for efficiency-optimal values  $D_1$  and  $D_2$ . Based on these results, the efficiency-optimized modulation scheme is developed in Section V and an efficiency-optimized converter design is proposed in Section VI. Finally, in Section VII, the analytically calculated efficiencies are verified with measured efficiencies obtained from an experimental setup.

#### II. AUTOMOTIVE DAB, WORKING PRINCIPLE

The basic technical data of the DAB used and depicted in Fig. 2 is listed below.

- PCB: four-layer PCB, 200  $\mu$ m copper on each layer.

- Switches (HV side): SPW47N60CFD.

- Switches (LV side): 8 × IRF2804 in parallel.

- DC capacitor (HV side):  $6 \times 470 \text{ nF/630 V}$  in parallel.

- DC capacitor (LV side):  $96 \times 10 \mu F/25 \text{ V/X5R}$  in parallel.

- Transformer core: two planar E58 cores.

- Transformer turns ratio, DAB inductance (cf. Section VI):

- phase shift modulation: n = 19: 1,  $L = 26.7 \mu H$ ;

- optimized modulation: n = 16: 1,  $L = 22.4 \mu H$ .

- Switching frequency:  $f_S = 100 \text{ kHz}$ .

The switching frequency is selected based on converter optimization results obtained for similar systems in order to achieve a high-efficiency and small-volume DAB converter:

- for a resonant LCC dc/dc converter with an input voltage of 320 V, an output voltage of 26 V, and an output power of 3.9 kW, a maximum power density of 13.3 kW/dm<sup>3</sup>, and converter efficiency of η = 93.7% are calculated for a switching frequency of 176 kHz [27];

- for a current doubler dc/dc converter (input voltage: 400 V, output voltage range: 48 V ≤ V<sub>2</sub> ≤ 56 V, output power: 5 kW), a maximum power density of 10.2 kW/dm³, and converter efficiency of η = 96.1% are calculated for a switching frequency of 92.9 kHz [28].

The switching frequency considered for the DAB converter,  $f_{\rm S}=100$  kHz, is selected close to 92.9 kHz, due to the impact of skin and proximity effects on the copper losses and due to high switching losses on the LV side. All semiconductor

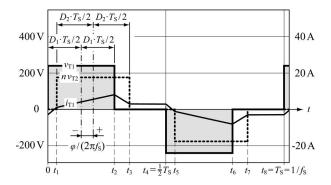

Fig. 3. The four DAB control parameters:  $\varphi$  denotes the phase shift between  $v_{\rm T1}$  and  $v_{\rm T2}$ ,  $D_{\rm 1}$ , and  $D_{\rm 2}$  are the respective duty cycles, and  $f_{\rm S}$  is the switching frequency. The phase shift  $\varphi$  is measured between the centers of the positive active time intervals of  $v_{\rm T1}$  and  $v_{\rm T2}$ ;  $\varphi>0$  applies in this figure. The selected definitions of  $\varphi$ ,  $D_{\rm 1}$ , and  $D_{\rm 2}$  can directly be used together with the fundamental component approximation approach, often used to analyze the DAB (e.g., [19]): the amplitudes of the fundamental components of  $v_{\rm T1}$  and  $v_{\rm T2}$  are  $V_{\rm 1,f}=4V_{\rm 1}\sin(\pi D_{\rm 1})/\pi$  and  $V_{\rm 2,f}=4V_{\rm 2}\sin(\pi D_{\rm 2})/\pi$ , respectively, and  $\varphi$  is the phase shift between the cosine-shaped functions of the fundamental components. Employed operating point:  $V_{\rm 1}=240$  V,  $V_{\rm 2}=11$  V,  $P_{\rm out}=500$  W (cf. (4)); n=16, L=22.4  $\mu{\rm H}$ .

switches are realized using MOSFETs: In respect of the selected switching frequency, and the required current and voltage ratings, MOSFETs are found to be superior to insulated-gate bipolar transistors.

The voltage-sourced full-bridge circuits on the HV side and on the LV side, depicted in Fig. 1(a), can be replaced by the respective voltage sources  $v_{\rm T1}$  and  $v_{\rm T2}$  to simplify the investigations on the DAB converter. Fig. 1(b) shows the converter model used and which is developed in [13]; it assumes:

- 1) negligible parasitic capacitances of the transformer, e.g.; no coupling capacitance between LV and HV sides;

- 2) all quantities being referred to the HV side;

- 3) constant supply voltages  $V_1$  and  $V_2$ .

The DAB converter model is parameterized in Section VI.

The DAB output power is adjusted by varying one or more of the four control parameters shown in Fig. 3 and listed below.

- phase shift between  $v_{T1}(t)$  and  $v_{T2}(t)$ :  $-\pi < \varphi < \pi$ ;

- duty cycle  $D_1$  of  $v_{T1}(t)$  with  $0 < D_1 \le 0.5$  [Fig. 3];

- duty cycle  $D_2$  of  $v_{T2}(t)$  with  $0 < D_2 \le 0.5$ ;

- switching frequency  $f_{\rm S}$ .

Phase shift modulation uses constant switching frequency and maximum duty cycles,  $D_1 = D_2 = 0.5$ , and the controller varies solely the phase shift  $\varphi$  to achieve the required power transfer [29]. Assuming a loss-less DAB converter and a negligible magnetizing current, the transferred power

$$P = P_1 = P_2 = \frac{nV_1V_2\varphi \cdot (\pi - |\varphi|)}{2\pi^2 f_{\rm S}L} \qquad \forall -\pi < \varphi < \pi \quad (1)$$

results [10], whereas  $L \approx L_1 + n^2 L_2$  applies. Maximum power transfer is achieved for  $\varphi = \pm \pi/2$  and the sign of P characterizes the power transfer direction

$$P > 0$$

: power transfer to the LV port(HV  $\rightarrow$  LV);

$P < 0$ : power transfer to the HV port(LV  $\rightarrow$  HV). (2)

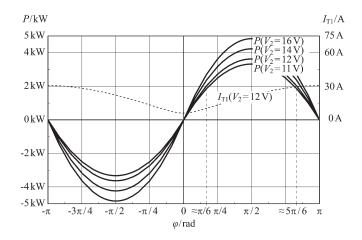

Fig. 4 depicts the power transfer characteristics of the DAB calculated with (1).

Fig. 4. DAB power transfer characteristics for phase shift modulation on the assumption of a loss-less converter  $(P=P_1=P_2),\ V_1=340$  V, and different voltages  $V_2;$  transformer rms current  $I_{\rm T1}$  for  $V_2=12$  V. The DAB is designed according to Section VI:  $n=19,\ L=26.7\ \mu{\rm H}.$  Maximum power transfer,  $|P|=P_{\rm max}(V_1,V_2),$  is achieved at  $\varphi=\pm\pi/2.$  For power levels  $|P|<P_{\rm max}(V_1,V_2),$  two solutions exist for  $\varphi$  within  $-\pi\leq\varphi<\pi.$  For  $|\varphi|>\pi/2,$  increased rms currents result in the high-frequency transformer, the DAB inductor L, and the semiconductor switches; therefore,  $|\varphi|<\pi/2$  is preferred.

The simplicity of phase shift modulation and the possibility of using half-bridge circuits to generate the high-frequency transformer voltages  $v_{\rm T1}(t)$  and  $v_{\rm T2}(t)$  are the main reasons for the wide use of this modulation method. Disadvantages are the limited operating range where low switching losses occur (soft-switching range [11]) and large rms currents in the high-frequency transformer for most operating points when the DAB is operated within wide input and/or output voltage ranges [14]. As a consequence, maximal converter efficiency is achieved only in a small area of the whole operating region (cf. Fig. 17).

#### III. DAB LOSS MODEL

In order to develop an efficiency-optimized modulation scheme (Sections IV and V), the DAB loss model detailed in [13] is employed. This loss model considers the semiconductor's conduction and switching losses, the copper and core losses of the inductor and the transformer, and the gate driver power dissipation. The total converter losses  $P_{\rm t} = P_1 - P_2$  are calculated with (13) in [13] and the efficiency is

$$\eta = \frac{|P_{\text{out}}|}{|P_{\text{out}}| + P_{\text{t}}}.\tag{3}$$

Moreover, the converter output power  $P_{\mathrm{out}}$  depends on the direction of power transfer

$$HV \rightarrow LV: \quad P_{\text{out}} = P_2$$

$LV \rightarrow HV: \quad P_{\text{out}} = P_1.$  (4)

In anticipation of the results obtained in Section IV, low conduction and low switching losses are particularly important to achieve a high efficiency of the given DAB converter. The conduction losses are calculated with the transformer rms currents  $I_{\rm T1}$  (HV side) and  $I_{\rm T2}$  (LV side) [13]. Due to the complexities of the employed electrical DAB model [Fig. 1(b)] and the employed converter loss model [13], only numerical

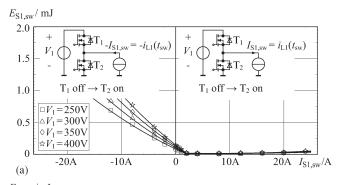

Fig. 5. Measured switching losses for a single-switching action (junction temperature:  $T_{\rm j}=25$  °C) (a) HV side and (b) LV side.  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$  indicate the switched current levels. Negative currents  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$  denote hard switching; for positive currents  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$  the condition for ZVS is satisfied. On the LV side, however, ZVS is not achieved for  $I_{\rm S2,sw}>50$  A due to parasitic inductances in series to the semiconductor switches leading to high switching losses there [13]. The depicted circuits illustrate the respective switching operation of a half bridge with regard to the sign of  $I_{\rm S1,sw}$  or  $I_{\rm S2,sw}$ .

TABLE I EXPRESSIONS REQUIRED TO OBTAIN  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$  From the Respective Instantaneous Transformer Currents  $i_{\rm T1}(t_{\rm sw})$  and  $i_{\rm T2}(t_{\rm sw})$  at a Switching Instant  $t_{\rm sw}$ ; e.g., in Fig. 3, at t=0, a Rising Edge of  $v_{\rm T1}$  Occurs and Thus, the HV Side Full Bridge Switches  $I_{\rm S1,sw}=-i_{\rm T1}(0)$

| HV Side, Edge Type of v <sub>T1</sub>  | $I_{ m S1,sw}$                                           |

|----------------------------------------|----------------------------------------------------------|

| Rising edge of $v_{T1}(t = t_{sw})$ :  | $I_{\rm S1,sw} = -i_{\rm T1}(t_{\rm sw})$                |

| Falling edge of $v_{T1}(t = t_{sw})$ : | $I_{\rm S1,sw} = i_{\rm T1}(t_{\rm sw})$                 |

| LV Side, Edge Type of v <sub>T2</sub>  | $I_{ m S2,sw}$                                           |

| Rising edge of $v_{T2}(t = t_{sw})$ :  | $I_{\rm S2,sw}=i_{\rm T2}(t_{\rm sw})$                   |

| Falling edge of $v_{T2}(t = t_{sw})$ : | $I_{\mathrm{S2,sw}} = -i_{\mathrm{T2}}(t_{\mathrm{sw}})$ |

solutions are feasible for  $I_{T1}$  and  $I_{T2}$ ; the numerical solver algorithm employed is outlined in Appendix A.

The switching losses are determined based on the measurement results presented in Fig. 5 and the respective instantaneous transformer currents  $i_{\rm T1}$  (HV side full bridge) and  $i_{\rm T2}$  (LV side full bridge) at the switching instant. The instantaneous transformer currents  $i_{\rm T1}$  and  $i_{\rm T2}$  are calculated with the procedure summarized in Appendix A. The expressions given in Table I are used to determine the respective values  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$ , required to evaluate the switching loss functions depicted in Fig. 5. The measurement results depicted in Fig. 5 represent the total switching loss energy of one-half bridge due to a single switching process: Negative currents  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$  denote hard switching and for positive currents  $I_{\rm S1,sw}$  and  $I_{\rm S2,sw}$ , the condition for ZVS is satisfied [13].

#### IV. NUMERICAL EFFICIENCY OPTIMIZATION

The optimization procedure shown here determines the duty cycles  $D_1$  and  $D_2$  and the phase shift angle  $\varphi$  with respect to maximal converter efficiency in steady-state operation for selected operating points defined by the DAB port voltages  $V_1$  and  $V_2$  and the required output power  $P_{\rm out}$  (cf. (4)). The output power for any  $0 < D_1 \leq 0.5, 0 < D_2 \leq 0.5$ , and  $-\pi < \varphi < \pi$  can either be calculated using an electric circuit simulator or with the procedure outlined in Appendix A.

The optimization procedure shown in this section can be used to obtain efficiency-optimal control parameters for arbitrary DAB converters. The calculated results are thereafter used in Section V in order to synthesize a new modulation scheme, which facilitates highly efficient operation of the investigated DAB converter.

In general, for a given operating point and given duty cycles, two solutions exist for the phase shift angle  $\varphi$ . For example, in Fig. 4, two phase shift angles,  $\varphi_1\approx\pi/6$  and  $\varphi_2\approx5\pi/6$ , generate an output power of 2 kW for  $V_1=340$  V and  $V_2=12$  V. The presented optimization procedure employs the minimal phase shift angle  $\varphi_{\min}$ , required to obtain the specified output power, according to

$$\varphi_{\min}(V_1, V_2, P_{\text{out}}, D_1, D_2) = \min |\varphi(V_1, V_2, P_{\text{out}}, D_1, D_2)| \cdot \operatorname{sgn} (\varphi(V_1, V_2, P_{\text{out}}, D_1, D_2))$$

(5)

since  $\varphi_{\min}$  allows for lower rms currents  $I_{T1}$  and  $I_{T2}$  and results in lowest conduction losses (cf.  $I_{T1}$  in Fig. 4). Thus, the considered converter efficiency  $\eta_0$ , calculated with (3) and (5), depends on the operating point and the two duty cycles

$$\eta_0(V_1, V_2, P_{\text{out}}, D_1, D_2)

= \eta(V_1, V_2, P_{\text{out}}, D_1, D_2, \varphi_{\min}(V_1, V_2, P_{\text{out}}, D_1, D_2)).$$

(6)

In order to determine the maximum efficiency at a given operating point, a numerical solver varies  $D_1$  and  $D_2$ :

$$\eta_{\text{opt}} = \max \left( \eta_0(V_1, V_2, P_{\text{out}}, D_1, D_2) \right)$$

$$\forall 0 < D_1 \le 0.5 \land 0 < D_2 \le 0.5. \quad (7)$$

(on the assumption of constant  $V_1$ ,  $V_2$ , and  $P_{out}$ ).

A thorough investigation of different operating points within the full specified operating range reveals essentially different results for  $V_1>nV_2$  and  $V_1< nV_2$ . Therefore, two meaningful examples are used to summarize the results of the investigations obtained for the DAB with n=16 and  $L=22.4~\mu{\rm H}$  designed in Section VI:

1)

$$V_1 > nV_2$$

:  $V_1 = 340$  V,  $V_2 = 12$  V,  $P_2 > 0$  [cf. (2)];

2)  $V_1 < nV_2$ :  $V_1 = 240$  V,  $V_2 = 16$  V,  $P_2 > 0$ .

A.

$$V_1 > nV_2$$

:  $V_1 = 340 \text{ V}$ ,  $V_2 = 12 \text{ V}$ ,  $P_2 > 0(HV \to LV)$

Analytical optimization of  $D_1$  and  $D_2$  with respect to the transformer rms current reveals that minimal rms current is achieved with the triangular current mode modulation [19] depicted in Fig. 6(a). Due to considerable switching losses,

<sup>&</sup>lt;sup>1</sup>The respective derivation considers the loss-less DAB model given in [11] and assumes an infinitely large transformer magnetizing inductance.

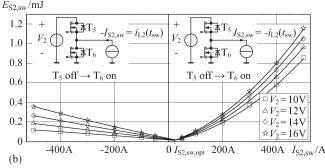

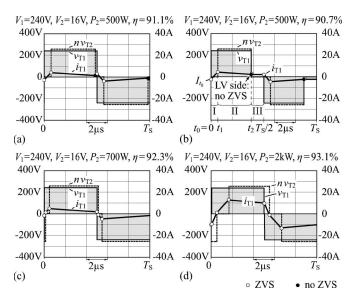

Fig. 6. Waveforms of  $v_{\rm T1}$ ,  $v_{\rm T2}$ , and  $i_{\rm T1}$  (cf. Fig. 1(a)) obtained for  $V_{\rm 1}=340$  V,  $V_{\rm 2}=12$  V, and different operating conditions; (a) triangular current mode modulation according to [19] and  $P_{\rm out}=500$  W; (b), (c) modulation at  $P_{\rm out}=500$  W: optimal and suboptimal converter efficiency,  $\eta_{\rm opt}$  and  $\eta_{\rm subopt}$  in Fig. 7(a), respectively; besides, (c) illustrates the modified triangular current mode modulation detailed in Section V-A1; and (d) optimal converter efficiency at  $P_{\rm out}=2$  kW. Employed DAB: n=16,  $L=22.4~\mu{\rm H}$ .

however, the efficiency obtained with the triangular current mode modulation is not maximal: At  $P_{\rm out}=500$  W,  $\eta=89\%$  results.

Fig. 7 depicts the calculated converter efficiencies within  $0 < D_1 \le 0.5$  and  $0 < D_2 \le 0.5$  and for different output power levels. The efficiency  $\eta_{\rm opt}$  marks the locations of the global efficiency maxima. Besides, for  $P_{\rm out} = 500$  W [Fig. 7(a)] and  $P_{\rm out} = 1$  kW [Fig. 7(b)], local efficiency maxima, marked with  $\eta_{\rm subopt}$ , are observed. According to Fig. 7, with increasing output power, the global and the local efficiency maxima shift toward  $D_2 = 0.5$ . Above a certain power level, only a global maximum remains; this is shown in Fig. 7(c) and (d) for  $P_{\rm out} = 1.5$  kW and  $P_{\rm out} = 2$  kW. Fig. 7 further indicates, that the local maximum depicted in Fig. 7(a) and (b) shifts toward  $D_2 = 0.5$  with increasing  $P_{\rm out}$  and becomes a global maximum in Fig. 7(c) and (d). As a consequence, a step in the efficiency-optimal control parameters  $D_1$ ,  $D_2$ , and  $\varphi$  can be observed in Fig. 8(a) between  $P_{\rm out} = 1.1$  kW and  $P_{\rm out} = 1.2$  kW.

The different properties of the most interesting operating points, i.e., operation at global and local efficiency maxima, need to be investigated in order to synthesize an efficiency-optimized modulation scheme. At the global efficiency maximum and  $P_{\rm out}=500$  W, a converter efficiency of  $\eta_{\rm opt}=92.4\%$  is achieved. There, the DAB converter experiences slightly increased conduction losses due to increased transformer rms currents; however, according to Figs. 5 and 6(b), minimal switching losses are achieved, since best possible instantaneous transformer currents (and thus switch currents) occur during switching:

- $I_{\text{S1,sw,1}} = -i_{\text{T1}}(t_1) \approx I_{\text{S1,sw,min}}$  (ZVS, cf. Appendix B);

- $I_{S1,sw,2} = +i_{T1}(t_2) > I_{S1,sw,min}$  (ZVS);

- $I_{S2,sw} = ni_{T1}(0) = n_{T1}(t_3) \approx 20 \text{ A (ZVS)}.$

Fig. 7. Converter efficiency determined according to Section III and (6) for  $0 < D_1 \le 0.5$ ,  $0 < D_2 \le 0.5$ , fixed operating voltages  $(V_1 = 340 \text{ V}, V_2 = 12 \text{ V})$ , and different power levels: (a)  $P_{\text{out}} = 500 \text{ W}$ , (b)  $P_{\text{out}} = 1 \text{ kW}$ , (c)  $P_{\text{out}} = 1.5 \text{ kW}$ , (d)  $P_{\text{out}} = 2 \text{ kW}$ . For low power levels, depicted in Fig. 7(a) and (b), a global maximum,  $\eta_{\text{opt}}$ , and a local maximum,  $\eta_{\text{subopt}}$ , occurs; for high power levels, Fig. 7(c) and (d), only a global maximum remains. Power transfer is not possible for combinations of  $D_1$  and  $D_2$  outside the indicated boundary. In that case, no solution exists for  $\varphi$  with respect to the required output power. On the contrary, the required output power can be achieved with any combination of  $D_1$  and  $D_2$  inside the indicated boundary. Employed DAB converter: n=16,  $L=22.4 \mu\text{H}$ .

Fig. 8. (a)  $D_1$ ,  $D_2$ , and  $\varphi$  required to achieve maximum converter efficiency for  $V_1=340$  V,  $V_2=12$  V, and power being transferred to the LV port: for  $P_{\rm out}$  between 1.1 and 1.2 kW, a step change in  $D_1$ ,  $D_2$ , and  $\varphi$  occurs; (b)  $D_1$ ,  $D_2$ , and  $\varphi$  for maximum converter efficiency,  $V_1=240$  V,  $V_2=16$  V, and power being transferred to the LV port: for  $P_{\rm out}$  between 600 and 700 W,  $D_2(P_{\rm out})$  exhibits a step change. Employed DAB converter: n=16,  $L=22.4~\mu{\rm H}$ .

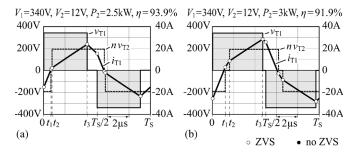

Fig. 9. Waveforms of  $v_{\rm T1}$ ,  $v_{\rm T2}$ , and  $i_{\rm T1}$  obtained for  $V_1=340$  V,  $V_2=12$  V, and efficiency-optimal operation at very high power levels (exceeding the rated power of 2 kW): (a)  $P_2=2.5$  kW and (b)  $P_2=3$  kW. Employed DAB converter: n=16, L=22.4  $\mu{\rm H}$ .

Due to the parasitic effective output capacitances of the HV MOSFETs used, a minimum current  $I_{\rm S1,sw,min}$  is required to obtain low switching losses on the HV side [13]; the optimal selection of  $I_{\rm S1,sw,min}$  is given in Appendix B. On the LV side, minimum switching losses are obtained for

$$I_{\rm S2,sw} \approx I_{\rm S2,sw,opt} \approx 20 \text{ A (cf. Fig. 5(b))}.$$

(8)

At the local efficiency maximum and  $P_{\rm out}=500~{\rm W},~{\rm a}$  converter efficiency of  $\eta=92.0\%$  is achieved. The LV side full bridge there exhibits switching losses due to hard-switching operation at  $t=t_3$  [Fig. 6(c)]. This operating mode is nonetheless employed for the suboptimal modulation scheme discussed in Section V, in order to avoid the step of  $D_1, D_2, {\rm and}~\varphi$  shown in Fig. 8(a), and is termed modified triangular current mode modulation.

According to Figs. 7(d) and 8(a), optimal operation at rated power  $P_{\rm out}=2$  kW is achieved with  $D_1=0.31$  and  $D_2=0.5$ . Fig. 6(d) depicts the corresponding current and voltage waveforms. Minimal reactive power is achieved on the LV side, since the instantaneous power  $p_2(t)$

$$p_2(t) = v_{T2}(t) \cdot i_{T2}(t) \approx v_{T2}(t) \cdot ni_{T1}(t)$$

(9)

does (virtually) not change sign during  $0 < t < T_{\rm S}$  [22] and thus, minimal conduction losses are achieved on the LV side. Moreover, minimal switching losses are achieved due to ZVS operation of the HV full bridge (cf. Table I) and due to the operation of the LV side full bridge with instantaneous switch currents  $I_{\rm S2,sw}$  close to zero.

The optimization algorithm increases  $D_1$  with increasing power levels and keeps  $D_2$  close to 0.5. This can be observed in Fig. 8(a) for power levels between 2 and 2.4 kW.

At very high power levels, finally, large phase shift angles and duty cycle values close to 0.5 are needed. As a consequence, the transformer rms currents rise considerably [19] and the instantaneous currents during switching increase. According to Fig. 8(a), the optimization algorithm reduces  $D_2$  for  $P_{\rm out} > 2.4$  kW. A reduction of the switching losses is achieved on the LV side with this, as illustrated in Fig. 9(b): Only two LV switches (e.g.,  $T_5$  and  $T_6$ ) switch  $I_{\rm S2,sw} > I_{\rm S2,sw,opt}$ ; the remaining two (e.g.,  $T_7$  and  $T_8$ ) switch  $I_{\rm S2,sw} \approx I_{\rm S2,sw,opt}$  (cf. Table I).

Fig. 10. Converter efficiency calculated for  $0 < D_1 \le 0.5, \, 0 < D_2 \le 0.5, \, V_1 = 240\,$  V,  $V_2 = 16\,$  V, and different power levels: (a)  $P_{\rm out} = 500\,$  W, (b)  $P_{\rm out} = 1\,$  kW, (c)  $P_{\rm out} = 1.5\,$  kW, and (d)  $P_{\rm out} = 2\,$  kW. Employed DAB:  $n = 16, \, L = 22.4\,$   $\mu$ H.

B.

$$V_1 < nV_2$$

:  $V_1 = 240 \text{ V}$ ,  $V_2 = 16 \text{ V}$ ,  $P_2 > 0(HV \to LV)$

The efficiency maps calculated for  $V_1=240~{\rm V}$  and  $V_2=16~{\rm V}$  (Fig. 10) are entirely different to the efficiency maps calculated in the previous Section IV-A. The optimization procedure varies  $D_2$  and keeps  $D_1$  close to 0.5. Again, local and global efficiency maxima occur and the efficiency-optimal duty cycle  $D_2$  exhibits a step change as shown in Fig. 8(b). However, compared to Section IV-A, the effect is less distinct and not visible in the efficiency maps depicted in Fig. 10.

The waveforms related to optimal DAB operation are shown in Fig. 11. Fig. 11(a) depicts the waveform of the transformer current  $i_{\rm T1}$  for  $P_{\rm out}=500$  W:  $i_{\rm T1}$  is nearly triangular and thus, low conduction losses result. Moreover, the instantaneous transformer currents during switching facilitate low switching losses due to the reasons given in Section IV-A and thus, a high total converter efficiency of 91.1% is achieved. However, similar to the DAB operation at  $V_1=340$  V,  $V_2=12$  V, and  $P_{\rm out}=500$  W, the discontinuous duty cycle function shown in Fig. 8(b) complicates the practical implementation.

A considerably reduced complexity is achieved if the modified triangular current mode modulation is used; typical current and voltage waveforms are depicted in Fig. 11(b). This modulation scheme facilitates a seamless transition between the operation with  $V_1 < nV_2$  and the operation with  $V_1 > nV_2$  due to the similarities to the modified triangular current mode modulation depicted in Fig. 6(c). The converter achieves nonetheless very high efficiency in the region of  $\eta_{\rm opt}$  (e.g.,  $\eta = 90.7\%$  for  $P_{\rm out} = 500$  W).

$<sup>^2</sup>$ More precisely, the modified triangular current mode modulation scheme facilitates a seamless transition between  $V_2 \leq V_{2, \mathrm{lim}}$  and  $V_2 \geq V_{2, \mathrm{lim}}$ , cf. Section V-A3: (21) and (22).

Fig. 11. Waveforms of  $v_{\rm T1}$ ,  $v_{\rm T2}$ , and  $i_{\rm T1}$  obtained for  $V_1=240~\rm V$ ,  $V_2=16~\rm V$ , and different operating conditions; (a) efficiency-optimal modulation at  $P_{\rm out}=500~\rm W$  ( $\eta_{\rm opt}$  in Fig. 10(a)); (b) modified triangular current mode modulation detailed in Section V-A-2 at  $P_{\rm out}=500~\rm W$ ; (c), (d) modulation for optimal converter efficiency at  $P_{\rm out}=700~\rm W$  (cf. Fig. 8(b)) and at  $P_{\rm out}=2~\rm kW$  ( $\eta_{\rm opt}$  in Fig. 10(d)), respectively. Employed DAB: n=16,  $L=22.4~\rm \mu H$ .

By use of  $P_{\rm out}=700$  W, depicted in Fig. 11(c), the DAB exceeds the maximum output power possible with the modulation scheme shown in Fig. 11(a). The optimization procedure there selects  $D_1=0.5$  and  $D_2<0.5$  in order to achieve ZVS on the HV side and low switching losses on the LV side (according to Fig. 11(c); however, only one LV side half bridge switches  $I_{\rm S2,sw}\approx I_{\rm S2,sw,opt}$ ; due to  $V_1< nV_2$ , it is unavoidable that the other LV half bridge switches  $I_{\rm S2,sw}>I_{\rm S2,sw,opt}$ ). This scheme remains unchanged with increasing output power. Fig. 11(d) illustrates the calculated voltage and current waveforms for  $P_{\rm out}=2$  kW. Again, large duty cycles and large phase shift angles are needed at very high power levels, which is shown in Fig. 8(b) (cf. Section IV-A), and the efficiency-optimal results for  $D_1$ ,  $D_2$ , and  $\varphi$  violate  $I_{\rm S2,sw}\approx I_{\rm S2,sw,opt}$  at very high power levels; nonetheless  $D_1=0.5$  remains.

#### V. SUBOPTIMAL MODULATION SCHEME

The findings obtained in the previous Section IV facilitate the development of an optimized modulation scheme in order to operate the given DAB close to the maximum achievable efficiency. The proposed modulation scheme therefore minimizes the impact of the most important DAB loss mechanisms:

- conduction losses;

- HV side switching losses (ZVS is required);

- LV side switching losses ( $I_{\rm S2,sw} \approx I_{\rm S2,sw,opt}$ , cf. (8)).

No closed-form solutions exist for the control parameters  $D_1$ ,  $D_2$ , and  $\varphi$ , due to the complexities of the electrical DAB model employed [Fig. 1(b)] and the converter loss model used [13]. Numerical solvers are used to evaluate the equation systems developed in this section in order to obtain values for  $D_1$ ,  $D_2$ , and  $\varphi$ . Currently, all solvers are implemented in Mathematica and a computer calculates the control parameters offline for 8192

different operating points according to the explanations given in this section. The results calculated are then postprocessed in order to reduce the effects of current-dependent time delays caused by the DAB hardware [30]. The control data so obtained is stored in a table that resides in the digital control part of the DAB converter i.e., a digital signal processor (DSP). The DSP finally uses linear interpolation to approximately determine the required control parameters [31].<sup>3</sup>

This description of the optimized modulation scheme is limited to a power transfer to the LV side; however, the principles discussed apply to power transfer in any direction and it is straightforward to extend the modulation scheme in order to permit a power transfer to the HV side. Furthermore, a negligible magnetizing current is considered, i.e.,  $i_{\rm T1}\approx i_{\rm T2}/n$  applies.

### A. Optimized DAB Operation at Low Power Levels: Modified Triangular Current Mode Modulation

According to Section IV, highly efficient converter operation close to  $\eta_{\rm opt}$  is achieved by the DAB converter with the modified triangular current mode modulation scheme. Typical current and voltage waveforms are shown in Fig. 6(c) for nominal converter operation.

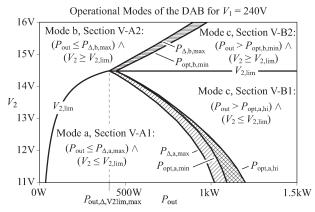

The original version of the triangular current mode modulation scheme distinguishes between  $V_2 < V_1/n$  and  $V_2 > V_1/n$  in order to calculate  $D_1$ ,  $D_2$ , and  $\varphi$ , due to essentially different characteristics of the transformer currents; the respective calculation is thoroughly discussed in [14], [19]. Detailed investigations show that the modified triangular current mode modulation scheme distinguishes between  $V_2 \le V_{2,\mathrm{lim}}$  (mode a) and  $V_2 \ge V_{2,\mathrm{lim}}$  (mode b), whereas

$$V_{2,\text{lim}} < V_1/n.$$

(10)

The actual computation of  $V_{2,\mathrm{lim}}$  is explained in Section V-A3, subsequent to the discussion of the modified triangular current mode modulation schemes; a typical characteristics of  $V_{2,\mathrm{lim}}$  is shown in Fig. 14. An analytical investigation of the modified triangular current mode modulation scheme reveals that  $V_{2,\mathrm{lim}} = V_1/n$  would be achieved for a loss-less converter and for  $-I_{t_0} = I_{t_1}$  in Fig. 6(c). However, based on the results of Section IV, i.e., due to the different switching loss characteristics of the HVMOSFETs and the LV MOSFETs,  $-I_{t_0} > 2$  A and  $I_{t_1} = I_{\mathrm{S2,sw,opt}}/n \approx 20/n = 1.25$  A are required on the HV side and on the LV side, respectively (cf. (8); n = 16 is assumed). Therefore, the inequality (10) results.

It is important to note that the modified triangular current mode modulation scheme achieves ZVS on the HV side; however, one hard-switching process per half-cycle occurs on the LV side, e.g., at  $t=t_3$  in Fig. 6(c) and at  $t=t_2$  in Fig. 11(b).

$^3\mathrm{The}$  actual implementation employs 16 values for  $V_1$ , 16 values for  $V_2$ , and 16 values for  $P_\mathrm{out}$  in either direction of power transfer. Due to the linear interpolation, a maximum absolute error of 58 W is calculated for the output power with the basic values being evenly distributed. Moreover, the resistive dividers employed to measure  $V_1$  and  $V_2$  consist of resistors with an accuracy of 0.1%. In order to eliminate the errors due to the linear interpolation and the voltage measurements, a current controller is required (cf. [29]).

1)  $V_2 \le V_{2,\lim}$  (mode a: Fig. 6(c)): During  $0 < t < t_0$ , both full bridges remain in their freewheeling states, i.e.,  $v_{\rm T1} =$  $v_{\rm T2}=0$ , and a negative transformer current  $i_{\rm T1}(t_0)=I_{t_0}$  enables ZVS at  $t = t_0$ ; subsequently, during  $t_0 < t < t_1$ , the HV full bridge applies  $v_{\rm T1} = V_1$ . The transformer current  $i_{\rm T1}$ increases to  $i_{\rm T1}(t_1) \approx I_{t_1} = I_{\rm S2,sw,opt}/n \approx 20$  A/n: At  $t = t_1$ , the LV full bridge switches to  $v_{\rm T2} = V_2$  and thereby generates minimal switching losses (cf. Fig. 5(b)). Due to  $V_1 > nV_2$ ,  $i_{\rm T1}$ continues to increase during  $t_1 < t < t_2$  until the HV full bridge switches to its freewheeling state at  $t = t_2$  (ZVS). During time interval III, the transformer current decreases to  $i_{\rm T1}(t_3) = -I_{t_0}$ . At  $t = t_3$ , the LV full bridge switches to  $v_{\rm T2} = 0$  (hard switching operation) and the remaining transformer current during  $t_3$  $t < t_4, i_{\rm T1}(t) = -I_{t_0}$ , enables ZVS for the HV full bridge at t = $t_4$ . During the second half-cycle  $(T_S/2 < t < T_S)$ , the voltage and current waveforms repeat with reverse sign.

The durations of the respective time intervals I, II, and III are calculated thus in order to

- provide the specified output power  $P_{\text{out}}$  (cf. (4));

- generate the freewheeling current  $I_{t_0} = -I_{\mathrm{S1,sw,min}}$  (enables ZVS on the HV side, cf. Appendix B);

- generate the current  $I_{t_1} = I_{\rm S2,sw,opt}/n$  (cf. (8)) to achieve low switching losses on the LV side.

The computation of the respective control parameters  $D_1$ ,  $D_2$ , and  $\varphi$  employs an approximate value of the duration of time interval I in Fig. 6(c),  $T_{\rm I}$ , in order to reduce the computational

$$T_{\rm I} = \frac{L \cdot (-I_{t_0} + I_{t_1})}{V_1} = \frac{L \cdot (I_{\rm S1,sw,min} + I_{\rm S2,sw,opt}/n)}{V_1}.$$

(11)

The calculation of  $D_1$ ,  $D_2$ , and  $\varphi$  employs

$$\frac{D_1}{2f_S} + \frac{|\varphi|}{2\pi f_S} = T_I + \frac{D_2}{2f_S} \Rightarrow D_1 = D_2 - \frac{|\varphi|}{\pi} + 2T_I f_S \quad (12)$$

for mode a, which can be derived from Figs. 3 and 6(c). A numerical search algorithm seeks suitable values  $\mathcal{D}_2$  and  $\varphi$  that meet the requirements

$$P_{\text{out}}(D_1, D_2, \varphi) = P_{\text{out,d}} \text{ and}$$

(13)

$$I_{t_0}(D_1, D_2, \varphi) = -I_{\text{S1,sw,min}}$$

$$\forall V_2 \le V_{2,\text{lim}} \land P_{\text{out}} \le P_{\triangle, \text{a,max}}$$

(14)

$$\forall V_2 \le V_{2,\lim} \land P_{\text{out}} \le P_{\triangle,\text{a,max}} \tag{15}$$

in order to achieve the designated output power  $P_{\text{out,d}}$  and the freewheeling current  $I_{\rm S1,sw,min}$ , cf. (50). The algorithm discussed in Appendix A calculates  $P_{\text{out}}$  and  $I_{t_0}$ .

Similar to the triangular current mode modulation scheme presented in [19], the maximum possible output power is limited according to (15). At  $P_{\text{out}} = P_{\triangle, \text{a,max}}$ , the expression  $D_1/2 + |\varphi|/(2\pi) + D_2/2 = 1/2$  applies (cf. Fig. 3 for  $t_3 =$  $T_{\rm S}/2$ ) and with (12), the equation system needed to solve for  $P_{\triangle,\mathrm{a,max}}$  becomes

$$[I_{t_0}(D_1, D_2) = -I_{S1,sw,min} \wedge D_2 = 0.5 - T_I f_S]$$

$\Leftrightarrow P_{out}(D_1, D_2) = P_{\triangle,a,max}.$  (16)

2)  $V_2 \ge V_{2,\text{lim}}$  (Mode b: Fig. 11(b)): During  $t_0 < t < t_1$ , the HV full bridge applies  $v_{\rm T1} = V_1$ , the LV full bridge remains in its freewheeling state, and the transformer currents increase; again,  $i_{T1}(t_0) = I_{t_0}$  enables ZVS on the HV side. At  $t = t_1$ , the LV full bridge switches to  $v_{\rm T2} = V_2$  and during  $t_1 < t < t_2$ , the transformer currents decrease due to  $V_1 < nV_2$ . At  $t = t_2$ , the transformer current  $i_{T1}(t_2)$  reaches  $-I_{t_0}$  and both full bridges simultaneously switch to the freewheeling states  $v_{\rm T1} =$  $v_{\rm T2} = 0$  (ZVS on the HV side, hard switching on the LV side).

The durations of the time intervals I and II are such that:

- the specified output power  $P_{\text{out}}$  (cf. (4)) is obtained

- the freewheeling current  $I_{t_0} = -I_{\rm S1,sw,min}$  is generated. The computation of  $D_1$ ,  $D_2$ , and  $\varphi$  employs

$$\frac{D_1}{2f_{\rm S}} = \frac{|\varphi|}{2\pi f_{\rm S}} + \frac{D_2}{2f_{\rm S}} \Rightarrow D_2 = D_1 - \frac{|\varphi|}{\pi}$$

(17)

which can be derived from Figs. 3 and 11(b). A numerical search algorithm determines the values for  $D_1$  and  $\varphi$  that satisfy (13) and (14) within

$$V_2 \ge V_{2,\text{lim}} \land P_{\text{out}} \le P_{\triangle,\text{b,max}}.$$

(18)

The maximum possible output power  $P_{\triangle,b,max}$  is obtained from (17) and  $D_1 = 0.5$ :

$$\left[ I_{t_0}(D_2, \varphi) = -I_{\text{S1,sw,min}} \wedge D_1 = 0.5 \wedge D_2 = 0.5 - \frac{|\varphi|}{\pi} \right]

\Leftrightarrow P_{\text{out}}(D_2, \varphi) = P_{\triangle, \text{b,max}}.$$

(19)

3) Calculation of  $V_{2,\text{lim}}$ : At  $V_2 = V_{2,\text{lim}}$ , both modified triangular current mode modulation schemes, i.e., mode a and mode b, can be used. The respective maximum possible power levels are identical there and are termed  $P_{\triangle, \mathrm{V2\,lim, max}}$

$$P_{\triangle, \text{V2} \text{lim,max}} = P_{\triangle, \text{a,max}}(V_2 = V_{2, \text{lim}})$$

=  $P_{\triangle, \text{b,max}}(V_2 = V_{2, \text{lim}}).$  (20)

At  $P_{\text{out}} = P_{\triangle,\text{V2}_{\text{lim,max}}}$ , for a given  $V_1$  and with (11), (16), and (19), the control parameters become constant and the numerical solver solely needs to vary  $V_2$  in order to satisfy  $I_{t_0} = -I_{\rm S1,sw,min}$  and to calculate  $V_{2,\rm lim}(P_{\triangle,\rm V2\,lim,max})$

$$\begin{split} &[I_{t_0}(V_2) = -I_{\mathrm{S1,sw,min}} \wedge D_1 = 0.5 \wedge D_2 = 0.5 - T_{\mathrm{I}} f_{\mathrm{S}} \\ & \wedge \varphi = \pi T_{\mathrm{I}} f_{\mathrm{S}} \mathrm{sgn}(P_{\mathrm{out,d}})] \\ \Leftrightarrow &[V_2 = V_{2,\mathrm{lim}}(P_{\triangle,\mathrm{V2\,lim,max}}) \wedge P_{\mathrm{out}} = P_{\triangle,\mathrm{V2\,lim,max}}]. \end{split} \tag{21}$$

The overview of all employed modulation schemes depicted in Fig. 14 shows that  $V_{2,\text{lim}}$  decreases with decreasing  $P_{\text{out}}$  <  $P_{\triangle, \text{V2} \text{ lim, max}}$ . Since  $I_{t_0} = -I_{\text{S1,sw,min}}$  needs to be satisfied for mode a and mode b, and with (11) and (17), the respective equation system needed to compute  $V_{2,\text{lim}}(P_{\text{out.d}})$  is

$$[P_{\text{out}}(D_1, V_2) = P_{\text{out,d}} \wedge I_{t_0}(D_1, V_2) = -I_{\text{S1,sw,min}}$$

$$\wedge \varphi = \pi T_1 f_{\text{S}} \operatorname{sgn}(P_{\text{out,d}}) \wedge D_2 = D_1 - \frac{|\varphi|}{\pi}$$

$$\Leftrightarrow V_2 = V_{2,\text{lim}}(P_{\text{out,d}}) \forall P_{\text{out,d}} < P_{\Delta,\text{V2} \text{lim,max}}.$$

(22)

A close inspection of the modulation schemes employed for  $P_{\text{out}} > P_{\triangle, \text{V2}_{\text{lim,max}}}$ , i.e., at high power levels, reveals that  $V_{2,\mathrm{lim}}(P_{\mathrm{out}})$  remains approximately equal to  $V_{2,\text{lim}}(P_{\triangle,\text{V2}\,\text{lim},\text{max}})$  (cf. Fig. 14).

#### B. Optimized DAB Operation at High Power Levels: Mode c

The duration of the freewheeling time interval used in the modified current mode modulation scheme decreases if the output power increases and reaches zero at  $P_{\rm out} = P_{\triangle,\rm a,max}$  for  $V_2 \leq V_{2,\rm lim}$  and at  $P_{\rm out} = P_{\triangle,\rm b,max}$  for  $V_2 \geq V_{2,\rm lim}$ . The results obtained in Section IV suggest a new modulation scheme to be used at high power levels, which complies with the conditions listed below.

- $v_{\text{T1}}(t)$  changes from  $V_1$  to  $-V_1$  during the time interval with constant voltage  $v_{\text{T2}}(t) = V_2$  or  $v_{\text{T2}}(t) = -V_2$ .

- $v_{\rm T2}(t)$  changes from  $V_2$  to  $-V_2$  during the time interval with constant voltage  $v_{\rm T1}(t) = V_1$  or  $v_{\rm T1}(t) = -V_1$ .

For example, Figs. 6(d), 9, and 11(c) and (d) satisfy these conditions; moreover, phase shift modulation (Section II) represents a special case and satisfies these conditions for all  $0<|\varphi|<\pi$ . The operation with this new modulation scheme is denoted DAB operating mode c.

It can be shown, e.g., based on Figs. 3 and 9(b), that the operation within mode c requires

$$\frac{|\varphi|}{2\pi} + \frac{D_2}{2} \ge \frac{D_1}{2} + \left(\frac{1}{2} - D_1\right) \lor \frac{D_1}{2} \ge \frac{|\varphi|}{2\pi} - \frac{D_2}{2}. \tag{23}$$

In summary,  $\varphi$  is limited according to

mode

$$c: 1 - (D_1 + D_2) \le |\varphi|/\pi \le D_1 + D_2$$

. (24)

Similar to Section V-A,  $D_1$ ,  $D_2$ , and  $\varphi$  are determined in a different way for  $V_2 \leq V_{2, \rm lim}$  and  $V_2 \geq V_{2, \rm lim}$ .

- 1)  $V_2 \le V_{2,\text{lim}}$ :  $D_1$  and  $D_2$  are selected according to the results depicted in Figs. 6(d), 7(d) and 8(a).

- D<sub>1</sub> ≤ 0.5 in order to achieve low switching losses: the HV side full bridge needs to be operated with ZVS and on the LV side, switching currents close to I<sub>S2,sw,opt</sub> (cf. (8)) result:

- $D_2 = 0.5$  (or  $D_2$  close to 0.5 for very high power levels, cf. Section IV-A) in order to achieve low transformer rms currents and low conduction losses.

The respective computation of  $D_1$  and  $D_2$  distinguishes between three different output power levels.

- 1)  $P_{\triangle,a,\max} < P_{\text{out}} \le P_{\text{opt,a,min}}$ : transition from mode a to high-power modulation.

- 2)  $P_{\text{opt,a,min}} < P_{\text{out}} \le P_{\text{opt,a,hi}}$ :  $D_1 \le 0.5$ ,  $D_2 = 0.5$ .

- 3)  $P_{\text{opt,a,hi}} < P_{\text{out}} \le P_{\text{max}}$ :  $D_1 = 0.5$ ,  $D_2 \le 0.5$  in order to achieve reduced switching losses on the LV side.

The power level  $P_{\triangle,a,\max}$  is given with (16),  $P_{\text{opt,a,min}}$ ,  $P_{\text{opt,a,hi}}$ , and  $P_{\max}$  are defined in this section.

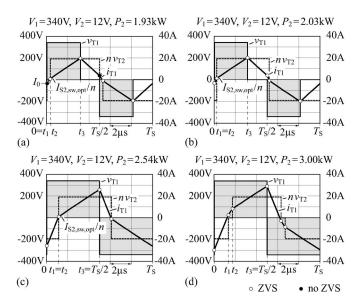

Both duty cycles  $D_1$  and  $D_2$  are less than 0.5 at  $P_{\rm out}=P_{\Delta,\rm a,max}$  [Fig. 12(a)]. Moreover, hard switching occurs on the LV side, e.g., at  $t=T_{\rm S}/2$  in Fig. 12(a).

According to the results obtained in Section IV, low conduction losses and low switching losses are achieved with  $D_2=0.5,\ i_{\rm T1}(0)\leq -I_{\rm S1,sw,min},\$ and  $i_{\rm T1}(t_1)=i_{\rm T1}(t_2)\approx I_{\rm S2,sw,opt}/n,$  which is given in Fig. 12(b). The respective output power  $P_{\rm opt,a,min}$  is higher than  $P_{\Delta,a,\rm max}$  and is computed with

$$[i_{\text{T1}}(t=0, D_1, \varphi) = -I_{\text{S1,sw,min}} \wedge i_{\text{T1}}(t=t_1, D_1, \varphi)$$

$$= I_{\text{S2,sw,opt}}/n \wedge D_2 = 0.5]$$

$$\Leftrightarrow P_{\text{out}}(D_1, \varphi) = P_{\text{opt,a,min}}.$$

(25)

Fig. 12. Calculated waveforms  $v_{\rm T1}(t)$ ,  $v_{\rm T2}(t)$ , and  $i_{\rm T1}(t)$  for DAB operation at  $V_1=340$  V and  $V_2=12$  V, using the optimized modulation scheme: (a)  $P_{\rm out}=1.93$  kW, (b)  $P_{\rm out}=2.03$  kW, (c)  $P_{\rm out}=2.54$  kW, and (d)  $P_{\rm out}=3.00$  kW; n=16, L=22.4  $\mu{\rm H}$ , and  $L_{\rm M}=1.9$  mH (thus,  $i_{\rm T1}\approx i_{\rm T2}/n$  applies); Fig. 12(a)–(c) depict the limits of the respective operating modes: (a)  $P_{\rm out}=P_{\triangle,a,{\rm max}}$ ; (b)  $P_{\rm out}=P_{\rm opt,a,min}$ ; (c)  $P_{\rm out}=P_{\rm opt,a,hi}$ .

$P_{

m opt,a,min} \approx 2$  kW applies for the given DAB converter at  $V_1 = 340$  V and  $V_2 = 12$  V. The control parameters  $D_1$ ,  $D_2$ , and  $\varphi$  for output power levels between  $P_{\triangle,a,\max}$  and  $P_{

m opt,a,min}$  are obtained from

$$P_{\text{out}}(D_{1}, D_{2}, \varphi) = P_{\text{out,d}}$$

$$i_{\text{T1}}(t = 0, D_{1}, D_{2}, \varphi) = I_{t_{0}}$$

$$i_{\text{T1}}(t = t_{1}, D_{1}, D_{2}, \varphi) = I_{\text{S2,sw,d}}/n$$

$$\forall V_{2} \leq V_{2,\text{lim}} \wedge P_{\triangle,\text{a,max}} < P_{\text{out}} \leq P_{\text{opt,a,min}}$$

(26)

whereas a linear transition is employed for the LV side switch current  $I_{\rm S2,sw,d}$ ,

$$I_{\rm S2,sw,d} = I_{\rm S2,sw,\triangle,a,max} + (I_{\rm S2,sw,opt} - I_{\rm S2,sw,\triangle,a,max}) \cdot \frac{P_{\rm out,d} - P_{\triangle,a,max}}{P_{\rm opt,a,min} - P_{\triangle,a,max}}$$

(27)

with  $I_{\rm S2,sw,\triangle,a,max} = n \cdot i_{\rm T1}(t=0,P_{\rm out}=P_{\triangle,a,max}) = n \cdot I_{t_0}$ . According to Fig. 8(a), for 2 kW <  $P_{\rm out}$  < 2.5 kW,  $D_2=0.5$  is approximately constant. In order to achieve low losses,  $D_1$  and  $\varphi$  are calculated in order to satisfy

$$P_{\mathrm{out}}(D_1, D_2 = 0.5, \varphi) = P_{\mathrm{out,d}}$$

and

$$i_{\mathrm{T1}}(t = t_1, D_1, D_2 = 0.5, \varphi) = I_{\mathrm{S2,sw,opt}}/n$$

$$\forall V_2 \leq V_{2,\mathrm{lim}} \wedge P_{\mathrm{opt,a,min}} < P_{\mathrm{out}} \leq P_{\mathrm{opt,a,hi}}.$$

(28)

The control parameters  $D_1$  and  $\varphi$  calculated with this equation system additionally guarantee ZVS on the HV side due to the high output power levels and due to  $V_2 \leq V_{2,\mathrm{lim}}$ . Moreover,  $D_1$  increases with increasing output power;  $D_1$  becomes equal to 0.5 at  $P_{\mathrm{out}} = P_{\mathrm{opt,a,hi}}$  [Fig. 12(c)]:

$$[i_{\text{T1}}(t=t_1,\varphi) = I_{\text{S2,sw,opt}}/n \land D_1 = 0.5 \land D_2 = 0.5]$$

$$\Leftrightarrow P_{\text{out}}(\varphi) = P_{\text{opt,a,hi}}. \quad (29)$$

Fig. 13. Calculated waveforms  $v_{\rm T1}(t), v_{\rm T2}(t)$ , and  $i_{\rm T1}(t)$  for DAB operation at  $V_1=240~{\rm V}$  and  $V_2=16~{\rm V}$ , using the optimized modulation scheme: (a)  $P_{\rm out}=895~{\rm W}$ , (b)  $P_{\rm out}=976~{\rm W}$ , and (c)  $P_{\rm out}=2.00~{\rm kW}; \ n=16, L=22.4~\mu{\rm H}$ , and  $L_{\rm M}=1.9~{\rm mH}$ ; Fig. 13(a) and (b) depict the limits of the respective operating modes: (a)  $P_{\rm out}=P_{\triangle,{\rm b,max}}$ ; (b)  $P_{\rm out}=P_{\rm opt,b,min}$ .

A reduced duty cycle  $D_2 < 0.5$  is employed on the LV side if the required output power level exceeds  $P_{\rm opt,a,hi}$  in order to reduce the switching losses. This can be observed in Fig. 12(d): At  $t=t_1$ , the current during switching is close to  $I_{\rm S2,sw,opt}$ . The duty cycle  $D_1=0.5$  remains constant in order to achieve low transformer rms currents and  $D_2$  and  $\varphi$  are determined with respect to maximum total efficiency

$$P_{\text{out}}(D_{1} = 0.5, D_{2}, \varphi) = P_{\text{out,d}}$$

$$\eta(D_{1} = 0.5, D_{2}, \varphi) = \max \left[ \eta(D_{1} = 0.5, D_{2}, \varphi) \right]$$

$$i_{\text{T1}}(t = t_{1}, D_{1} = 0.5, D_{2}, \varphi) > I_{\text{S2,sw,opt}}/n$$

$$\forall V_{2} \leq V_{2,\text{lim}} \land P_{\text{opt,a,hi}} < P_{\text{out}} \leq P_{\text{max}}.$$

(30)

Analytical investigations show that maximum output power  $P_{\rm max}$  is achieved with phase shift modulation. The respective value is computed with a numerical maximum search

$$(D_1 = 0.5 \land D_2 = 0.5) \Leftrightarrow P_{\text{max}} = \max \left[ P_{\text{out}}(\varphi) \right]. \quad (31)$$

- 2)  $V_2 \ge V_{2,\text{lim}}$ :  $D_1$  and  $D_2$  are selected according to Fig. 8(b) at high power levels, Figs. 10(d) and 11(d).

- $D_1 = 0.5$  in order to achieve low conduction losses.

- $D_2 \le 0.5$  in order to achieve low switching losses.

The computation of  $D_1$  and  $D_2$  distinguishes between two different output power levels:

- 1)  $P_{\triangle, b, max} < P_{out} \le P_{opt, b, min}$ : transition from mode b to high-power modulation,

- 2)  $P_{\rm opt,b,min} < P_{\rm out} \le P_{\rm max}$ : operation in mode c with  $D_1 = 0.5, D_2 \le 0.5$ .

The power level  $P_{\triangle,b,max}$  is given with (19),  $P_{opt,b,min}$  is defined with (32) in this section, and  $P_{max}$  is defined with (31).

At  $P_{\rm out}=P_{\triangle,{\rm b,max}}$ , the duty cycles  $D_1=0.5$  and  $D_2<0.5$  result; typical current and voltage waveforms are shown in Fig. 13(a). Furthermore, hard switching occurs on the LV side at  $t=t_1=0$ . With increasing output power,  $D_2$  and  $\varphi$

Fig. 14. DAB operating modes for  $V_1=240$  V, different voltages  $V_2$ , different output power levels  $P_{\rm out}$ , n=16, and  $L=22.4~\mu H$ .

increase, and the current  $i_{\rm T1}(t_1)$  becomes equal to  $I_{\rm S2,sw,opt}/n$  at  $P_{\rm out}=P_{\rm opt,b,min}$  as shown in Fig. 13(b):

$$[i_{\text{T1}}(t=0, D_2, \varphi) = -I_{\text{S1,sw,min}} \wedge i_{\text{T1}}(t=t_1, D_2, \varphi)$$

$$= I_{\text{S2,sw,opt}}/n \wedge D_1 = 0.5]$$

$$\Leftrightarrow P_{\text{out}}(D_2, \varphi) = P_{\text{opt,b,min}}.$$

(32)

For  $P_{\triangle,\mathrm{b,max}} < P_{\mathrm{out}} \leq P_{\mathrm{opt,b,min}}$ , a numerical search algorithm seeks suitable values for  $D_2$  and  $\varphi$  to satisfy

$$P_{\rm out}(D_1 = 0.5, D_2, \varphi) = P_{\rm out,d} \text{ and } i_{\rm T1}(t = t_1, D_1 = 0.5, D_2, \varphi) = I_{\rm S2,sw,d}/n$$

$$\forall V_2 \ge V_{\rm 2,lim} \land P_{\triangle,\rm b,max} < P_{\rm out} \le P_{\rm opt,b,min}.$$

(33)

A linear transition is used to determine the LV side switch current  $i_{\rm T1}(t_1) = I_{\rm S2.sw,d}/n$

$$I_{\rm S2,sw,d} = I_{\rm S2,sw,\triangle,b,max} + (I_{\rm S2,sw,opt} - I_{\rm S2,sw,\triangle,b,max}) \cdot \frac{P_{\rm out,d} - P_{\triangle,b,max}}{P_{\rm opt,b,min} - P_{\triangle,b,max}}; \quad (34)$$

$I_{\rm S2,sw,\triangle,b,max}$  is equal to  $n \cdot i_{\rm T1}(0)$  at  $P_{\rm out} = P_{\triangle,\rm b,max}$ , e.g.,  $I_{\rm S2,sw,\triangle,b,max} \approx 16 \cdot (-3~{\rm A}) \approx -50~{\rm A}$  in Fig. 13(a).

The maximum achievable output power  $P_{\rm max}$  is again calculated with (31).  $D_1=0.5$  remains for output power levels between  $P_{\rm opt,b,min}$  and  $P_{\rm max}$ , and  $D_2$  and  $\varphi$  are adjusted in order to obtain maximum efficiency

$$P_{\text{out}}(D_{1} = 0.5, D_{2}, \varphi) = P_{\text{out,d}}$$

$$\eta(D_{1} = 0.5, D_{2}, \varphi) = \max \left[ \eta(D_{1} = 0.5, D_{2}, \varphi) \right]$$

$$i_{\text{T}1}(t = t_{1}, D_{1} = 0.5, D_{2}, \varphi) > I_{\text{S2,sw,opt}}/n$$

$$\forall V_{2} \geq V_{2,\text{lim}} \land P_{\text{opt,b,min}} < P_{\text{out}} \leq P_{\text{max}}.$$

(35)

Fig. 13(c) shows the corresponding current and voltage waveforms in mode c for  $V_1=240$  V,  $V_2=16$  V(>  $V_{2,\rm lim}=14.5$  V), and  $P_{\rm out}=2$  kW.

#### C. Suboptimal Modulation Scheme, Summary, and Results

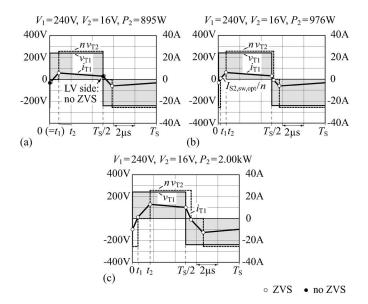

Fig. 14 presents an overview of the operating modes detailed in this section for  $V_1=240~\rm{V}, 11~\rm{V} \le V_2 \le 16~\rm{V}, 0 \le P_{\rm out} \le 1.5~\rm{kW}, n=16,$  and  $L=22.4~\rm{\mu H}.$

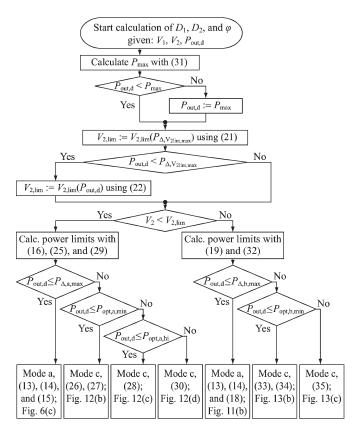

Fig. 15. Flowchart used to determine the correct equation system of the suboptimal modulation scheme and to compute  $D_1$ ,  $D_2$ , and  $\varphi$ .

The flowchart depicted in Fig. 15 illustrates the algorithm which is needed to choose the correct equation system: First, the designated output power  $P_{\mathrm{out,d}}$  is limited to the maximum output power  $P_{\mathrm{max}}$ , then  $V_{2,\mathrm{lim}}$  is calculated according to Section V-A3 and the appropriate equation system is selected based on the present value of the port voltage  $V_2$  and the value of  $P_{\mathrm{out,d}}$ . Finally, the control parameters  $D_1$ ,  $D_2$ , and  $\varphi$  are computed by solving the respective equation system.

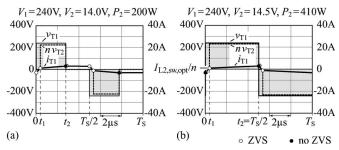

A little example is used to clarify the calculation of  $D_1$ ,  $D_2$ , and  $\varphi$ ; this example employs the given DAB converter with n=16 and  $L = 22.4 \mu H$ ,  $V_1 = 240 \text{ V}$ ,  $V_2 = 12 \text{ V}$ , and  $P_{\text{out,d}} =$ 200 W. In a first step, the maximum power is calculated according to (31) since  $P_{\text{out,d}}$  needs to be limited to  $P_{\text{max}}$ ;  $P_{\text{max}} =$  $2.3~\mathrm{kW}$  results and thus,  $P_{\mathrm{out,d}} = 200~\mathrm{W}$  remains. In a second step,  $V_{2,\rm lim}$  is calculated; therefore, (21) is solved. The results are  $V_{2,\text{lim}}(P_{\triangle,\text{V2}\,\text{lim},\text{max}}) = 14.5 \text{ V}$  and  $P_{\triangle,\text{V2}\,\text{lim},\text{max}} =$ 410 W. The corresponding current and voltage waveforms are shown in Fig. 16(b). Since  $P_{\text{out,d}} < P_{\triangle,\text{V2} \text{lim,max}}$  applies,  $V_{2,\mathrm{lim}}(P_{\mathrm{out,d}}=200~\mathrm{W})$  needs to be determined using (22). The calculated solution is  $V_{2,\text{lim}}(200 \text{ W}) = 14.0 \text{ V}$ ; Fig. 16(a) illustrates the respective waveforms. Due to  $V_2 = 12 \text{ V} <$  $V_{2,\text{lim}} = 14.0 \text{ V}$ , either mode a or mode c applies (Fig. 14). (16) yields  $P_{\triangle,\mathrm{a,max}} = 927~\mathrm{W}$  and thus, mode a is used. The control parameters are finally obtained from (13)–(15):  $D_1 = 0.20$ ,  $D_2 = 0.19$ , and  $\varphi = 0.18$ .

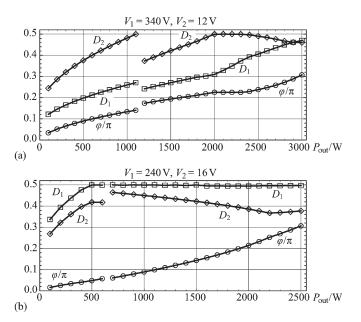

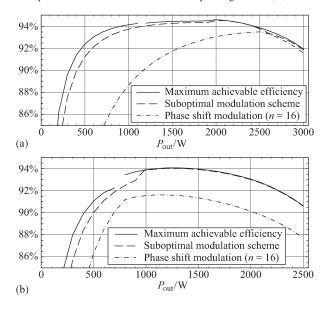

The calculated efficiencies for power being transferred to the LV port are shown in Fig. 17 for  $V_1=340~\rm{V},~V_2=12~\rm{V}$  [Fig. 17(a)] and  $V_1=240~\rm{V},~V_2=16~\rm{V}$  [Fig. 17(b)]: with phase shift modulation, high efficiency is only achieved for

Fig. 16. Current and voltage waveforms for  $V_1=240~{\rm V}$  and  $V_2=V_{2,{\rm lim}}$ , i.e., at the transition between mode a and mode b: (a)  $P_2=200~{\rm W}$ , (b)  $P_2=P_{\triangle,{\rm V2\,lim,max}}=410~{\rm W}$  (cf. (21)); at  $P_2=P_{\triangle,{\rm V2\,lim,max}}$ , the DAB is operated at the transition between the operating modes a, b, and c.

Fig. 17. Efficiency calculated for different modulation schemes: (a)  $V_1=340$  V,  $V_2=12$  V; (b)  $V_1=240$  V,  $V_2=16$  V. Highly efficient converter operation, close to maximum efficiency, is achieved with the suboptimal modulation scheme (n=16,  $L=22.4~\mu H$ ).

$V_1=340~{\rm V},\,V_2=12~{\rm V},\,{\rm and}\,P_{\rm out}>2.5~{\rm kW}.$  In contrast, with the suboptimal modulation scheme detailed in this section, the DAB converter operates close to the maximal achievable efficiency. Due to the use of the modified triangular current mode modulation depicted in Figs. 6(c) and 11(b) the efficiency is approximately 1%–2% below the maximum possible efficiency for  $P_{\rm out}<1000~{\rm W}$  and less than 0.5% below the maximum achievable efficiency for  $P_{\rm out}>1000~{\rm W}$  [Fig. 17(a)]; moreover, at  $P_{\rm out}\approx P_{\rm opt,a,hi}(29)$ , reduced efficiency is observed ( $P_{\rm out}\approx 2.6~{\rm kW}$  in Fig. 17(a)).

#### VI. OPTIMIZED DAB CONVERTER DESIGN

The design of the DAB is an iterative process: In a first step, appropriate values for n and L are assumed (e.g., according to [11]) and approximate values of the component stresses, i.e., maximum blocking voltages, maximum rms currents, and maximum magnetic field densities, are calculated with a simple DAB converter model. The results obtained enable a first selection of the DAB converter components, e.g., semiconductor switches, transformer core. Thereafter, the DAB loss model (Section III) is parameterized in order to permit an accurate prediction of the converter efficiency [13].

#### A. Design Procedure

The focus of this converter design is on the appropriate choice of the converter inductance L and the transformer turns ratio n in order to obtain maximum average converter efficiency  $\overline{\eta}$ . The design procedure therefore considers the DAB outlined in Section II, i.e., the semiconductor switches, the transformer core, and the dc capacitors are given. The average efficiency  $\overline{\eta}$  is calculated over 36 different operating points

$$\overline{\eta} = \frac{1}{36} \sum_{i=1}^{3} \sum_{j=1}^{3} \sum_{k=1}^{4} \left( \eta |_{V_1 = \vec{V}_{1,i}, V_2 = \vec{V}_{2,j}, P_{\text{out}} = \vec{P}_{\text{out},k}} \right), (36)$$

$$\vec{V}_1 = (240 \text{ V} \quad 340 \text{ V} \quad 450 \text{ V}), \tag{37}$$

$$\vec{V}_2 = (11 \text{ V} \quad 12 \text{ V} \quad 16 \text{ V}),$$

(38)

$$\vec{P}_{\text{out}} = (-2 \text{ kW} - 1 \text{ kW} 1 \text{ kW} 2 \text{ kW}).$$

(39)

Thus, the proposed design method emphasizes on operation with nominal voltages  $V_1$  and  $V_2$ , but also includes operation with minimum and/or maximum voltages  $V_1$  and  $V_2$ , i.e., the edges of the specified voltage ranges. Bidirectional operation and part load operation are considered due to (39).<sup>4</sup>

Additionally, the magnetizing inductance  $L_{\rm M}$  may be included in the design process: Increased magnetizing currents improve the ZVS properties of the DAB [11]; additionally, however, the rms values of the transformer currents  $i_{\rm T1}$  and  $i_{\rm T2}$  increase, which increases the copper losses and the conduction losses. Therefore, and due to the measured switching loss characteristics shown in Fig. 5, the investigated DAB converter shows highest average efficiency if the magnetizing currents are negligibly small. Moreover, the values of the dc capacitors  $C_{\rm DC1}$  and  $C_{\rm DC2}$  are not included in the design process, since the employed converter model considers constant dc voltages  $V_1$  and  $V_2$ . Thus,  $C_{\rm DC1}$  and  $C_{\rm DC2}$  can be selected independent of n and L, provided that the ac voltage superimposed on  $V_1$  and  $V_2$  is negligible.

#### B. Model Parameterization

The loss model outlined in Section III is parameterized for n=24 and is not readily applicable for  $n \neq 24$ ; however, for  $n \neq 24$ , most parameters of the employed DAB loss model remain unchanged, i.e., conduction losses caused from MOSFETs and PCB, switching losses, power demand of the auxiliary power. The remaining components are the highfrequency transformer and the additional converter inductance  $L_{\rm HV}$ , placed on the HV side in series to the transformer and required to provide the total converter inductance L. Analytical calculations show that the transformer parameters, i.e., winding resistances  $R_{\rm tr1}$  (HV side) and  $R_{\rm tr2}$  (LV side), winding stray inductances  $L_{\rm tr1}$  (HV side) and  $L_{\rm tr2}$  (LV side), and the transformer magnetizing inductance  $L_{\rm M}$ , are approximately proportional to the square of the employed number of turns for a given transformer core. The inductor  $L_{\rm HV}$  needs to be designed separately for each combination of n and L. An automated

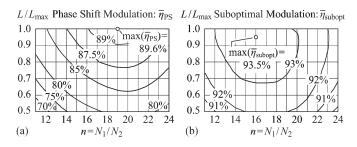

Fig. 18. (a) Calculated average efficiencies for phase shift modulation, different transformer turns ratios  $n=N_1/N_2$ , and different DAB inductances L ( $L_{\rm max}$  denotes the maximum allowable inductance with respect to the given converter specifications, cf. (1); e.g., for n=19,  $L_{\rm max}=26.7~\mu{\rm H}$  is determined); (b) calculated average efficiencies for the suboptimal modulation scheme;  $L_{\rm max}=23.6~\mu{\rm H}$  is calculated for n=16. Table II summarizes the design results.

design script, based on explanations given in [32], is used to design the inductor, to calculate the respective copper and core losses, and to determine its equivalent loss resistance  $R_{L_{\rm HV}}$ .

The resistance and inductance values employed for the electrical converter model shown in Fig. 1(b) and given with (40)–(44) are based on measurement results obtained from the final DAB prototype [13].

$$R_{1} = R_{HV} + R_{tr1}$$

$$= \underbrace{166 \text{ m}\Omega}_{\text{HV MOSFETs}} + \underbrace{R_{L_{HV}}}_{\text{resistance of the external inductor } L_{HV}$$

$$+ \underbrace{\frac{N_{1}^{2}}{24^{2}} \cdot 93 \text{ m}\Omega}_{\text{transformer,HV side}}$$

(40)

$$R_{2} = R_{\text{LV}} + R_{\text{tr}2}$$

$$= \underbrace{1.18 \text{ m}\Omega}_{\text{LV MOSFETs.PCB}} + \underbrace{273 \mu\Omega}_{\text{transformer LV side}}$$

(41)

$$L_{1} = L_{\text{HV}} + L_{\text{tr1}}$$

$$= \underbrace{L_{\text{HV}}}_{\text{external inductor}} + \underbrace{\frac{N_{1}^{2}}{24^{2}} \cdot 5 \, \mu \text{H}}_{\text{stray ind.,HV side}}$$

(42)

$$L_{2} = L_{\text{LV}} + L_{\text{tr}2}$$

$$= \underbrace{5 \text{ nH}}_{\text{PCB,MOSFETs}} + \underbrace{8.7 \text{ nH}}_{\text{stray ind.,LV side}}$$

(43)

$$L_{\rm M} = \frac{N_1^2}{24^2} L_{\rm M}(N_1 = 24)$$

$$= \frac{N_1^2}{24^2} \cdot 4.3 \text{ mH}.$$

(44)

#### C. Design Results for n and L

The average efficiencies calculated for phase shift modulation and different values n and  $L/L_{\rm max}$  are shown in Fig. 18(a): For n=19 and  $L=L_{\rm max}$ , the maximum average efficiency  ${\rm max}(\overline{\eta}_{\rm PS})=89.6\%$  is achieved. The value  $L_{\rm max}$  denotes the upper limit for L with respect to the specified output power, cf. (1), and depends on the turns ratio n; for n=19,  $L_{\rm max}=26.7~\mu{\rm H}$  is calculated. The respective maximum transformer rms currents are  $I_{\rm T1}=15.6~{\rm A}$  (HV side) and  $I_{\rm T2}=294~{\rm A}$  (LV side). Hard-switching operation of the HV side full bridge occurs for certain operating points [11] and considerably reduces

$<sup>^4</sup>$ If a dedicated evaluation criteria is specified, then (36)–(39) need to be modified accordingly; consequently, different values for n and L may result.

# TABLE II DESIGN SUMMARY FOR THE TWO DIFFERENT MODULATION SCHEMES; $I_{\rm T1}$ and $I_{\rm T2}$ Denote the RMS Values of the Respective Transformer Currents (HV and LV Sides); $I_{\rm C,DC1}$ and $I_{\rm C,DC2}$ are the Respective Capacitor RMS Currents in $C_{\rm DC1}$ and $C_{\rm DC2}$ [on the Assumption of Constant Currents $I_1$ and $I_2$ in Fig. 1(a)]; $\hat{B}_{\rm tr}$ Denotes the Peak Flux Density in the Transformer Core

| Property                | Phase Shift Mod. | Suboptimal Mod. |

|-------------------------|------------------|-----------------|

| L                       | 26.7 μΗ          | 22.4 μΗ         |

| n                       | 19               | 16              |

| $\max(I_{\mathrm{T1}})$ | 15.6 A           | 15.1 A          |

| $\max(I_{T2})$          | 294 A            | 240 A           |

| $\max(I_{C,DC1})$       | 14.9 A           | 12.1 A          |

| $\max(I_{C,DC2})$       | 245 A            | 138 A           |

| $\max(\hat{B}_{tr})$    | 142 mT           | 129 mT          |

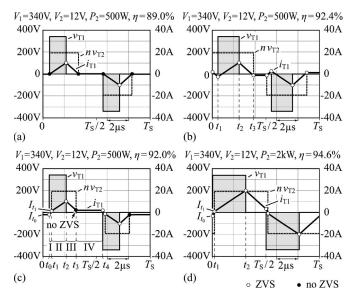

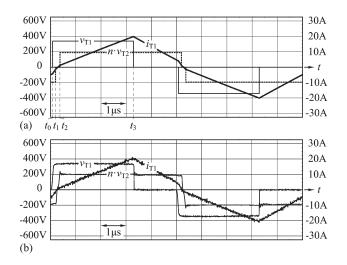

Fig. 19. (a) Calculated and (b) measured voltage and current waveforms obtained with the optimized modulation scheme for  $V_1=340~\rm V, V_2=12~\rm V,$   $P_2=2~\rm kW, n=16,$  and  $L=22.4~\rm \mu H;$  with the DAB model depicted in Fig. 1(b) and the loss model presented in Section III and [13], good matching between calculated and measured waveforms is achieved.

the converter efficiency (cf. Fig. 5(a); this typically occurs at low-load conditions, e.g., at  $V_1=240~\rm{V},~V_2=16~\rm{V},$  and  $P_{\rm out}=200~\rm{W})$ . The capacitor rms currents reach values of up to 245 A on the LV side (Table II).

The average efficiency achieved increases considerably by using the suboptimal modulation scheme [Fig. 18(b)]: for n=16 and  $L=22.4~\mu\mathrm{H},~\bar{\eta}_{\mathrm{subopt}}$  is 93.5%. Compared to phase shift modulation, reduced maximal transformer rms currents (HV side: 15.1 A, LV side: 240 A) and reduced capacitor rms currents are achieved (138 A; cf. Table II). Moreover, the HV side full bridge operates with ZVS within the full specified voltage and power ranges.

#### VII. RESULTS

The procedure outlined in Appendix A is used to calculate the transformer current waveforms  $i_{\rm T1}$  and  $i_{\rm T2}$ , which need to be known in detail in order to predict the conduction losses, the copper losses, and the switching losses [13]. Measured and calculated voltage and current waveforms for nominal operation are shown in Fig. 19. There, the calculated and measured waveforms of  $i_{\rm T1}$  and  $v_{\rm T1}$  match closely; solely the depicted

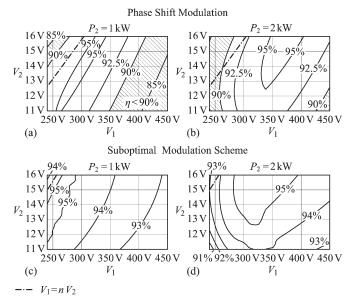

Fig. 20. Efficiencies calculated for power being transferred to the LV port: (a) and (b) phase shift modulation with  $P_2=1$  kW and  $P_2=2$  kW ( $n=19,\,L=26.7~\mu\rm H)$ ; (c) and (d) suboptimal modulation with  $P_2=1$  kW and  $P_2=2$  kW ( $n=16,\,L=22.4~\mu\rm H)$ ; for the suboptimal modulation scheme, Fig. 20(c) and (d), unsteady contour lines result due to the employed efficiency calculation method which considers interpolation errors (by reason of the linear interpolation algorithm used in the DSP, cf. Section V, [31]) in order to get as close as possible to the actual efficiency obtained with the DAB hardware prototype. Hatched areas denote  $\eta<90\%$ .

waveforms of  $v_{\rm T2}$  are slightly different. This difference is due to the interaction of the dead time interval (LV side:  $T_{\rm d}=240\,$  ns), employed to prevent a shoot through in the half-bridges, and the switching process at  $t=t_1$  close to the zero crossing of  $i_{\rm T1}(\approx i_{\rm T2}/n)$  (cf. Fig. 2 in [30]). Even though, the control parameters used for the DAB hardware compensate for the respective time delays, minor errors still occur. A more advanced calculation procedure—e.g., an electrical circuit simulator—may be used in order to further improve the quality of the predicted waveforms.

Fig. 20 (calculated efficiency maps) allows for a comparison between the efficiencies obtained for phase shift modulation and the suboptimal modulation scheme. The achieved efficiency improvement is particularly obvious for  $P_2=1\,$  kW (power is transferred to the LV port, cf. (2)): With phase shift modulation,  $\eta>90\%$  is only achieved within a limited band; the calculated minimum efficiency is 80.5% at  $V_1=450\,$  V and  $V_2=11\,$  V in Fig. 20(a). The minimum efficiency for  $P_2=1\,$  kW is 92.2% at  $V_1=450\,$  V and  $V_2=11\,$  V with the suboptimal modulation scheme [Fig. 20(c)]. For  $P_2=2\,$  kW, the converter efficiency achieved increases considerably: With phase shift modulation, the minimum efficiency is 84.6% [Fig. 20(b):  $V_1=240\,$  V,  $V_2=16\,$  V] and with the suboptimal modulation scheme  $\eta>90.2\%$  is achieved [Fig. 20(d); minimum at  $V_1=240\,$  V and  $V_2=11\,$  V].

The converter efficiency is measured for the suboptimal modulation scheme and different operating points in order to verify the calculated results. Fig. 21 illustrates the result (the  $\Box$  symbols indicate measured values and solid lines denote calculated results). The results depicted show good matching between calculated and measured results for  $P_2 > 500$  W. At

Fig. 21. Predicted efficiencies (solid lines) and measured efficiencies ( $\Box$ ) obtained with the optimized modulation scheme and power being transferred from the HV port to the LV port: (a)  $V_1=340$  V,  $V_2=12$  V, (b)  $V_1=240$  V,  $V_2=11$  V, (c)  $V_1=240$  V,  $V_2=16$  V, (d)  $V_1=450$  V,  $V_2=11$  V, (e)  $V_1=450$  V,  $V_2=16$  V; employed DAB converter: n=16 and  $L=22.4~\mu\mathrm{H}$ . The efficiencies are calculated with the DAB loss model presented in Section III and [13]; the efficiency measurement is carried out at an ambient temperature of  $T_{\rm A}=25~{\rm ^{\circ}C}$ .

very low power levels, i.e.,  $P_2 \approx 250$  W, uncertainties in the predicted loss components accumulate and cause a maximum difference between calculated and predicted efficiencies of 4%; still, the loss model (Section III) correctly predicts the trends of the efficiencies at low power levels.

The shown results are obtained for a DAB converter with a constant switching frequency of 100 kHz. Detailed analytical investigations show that the presented suboptimal modulation scheme also enables highly efficient converter operation for a switching frequency different to 100 kHz; solely the values  $I_{\rm S1,sw,min}$  and  $I_{\rm S2,sw,opt}$  need to be adjusted.  $I_{\rm S1,sw,min}$  and  $I_{\rm S2,sw,opt}$  decrease with decreasing switching frequency and approach zero if the switching frequency approaches zero, since this selection reduces the rms currents in the transformer and in the switches. A noticable effect, however, requires a very much reduced switching frequency (e.g.,  $f_{\rm S}=20$  kHz) being used for the given hardware setup due to the present switching losses shown in Fig. 5.

The suboptimal modulation scheme facilitates reduced transformer rms currents according to the results listed in Table II. As a consequence, the given DAB converter could be operated at a maximum output power higher than 2 kW without considerably changing the hardware: the suboptimal modulation scheme reaches the maximum transformer current of phase shift modulation,  $I_{\rm T2}=294$  A, at  $|P_{\rm out}|=2.5$  kW with n=16 and  $L=17.7~\mu{\rm H}$ . The respective average efficiency, calculated for  $\vec{P}_{\rm out}=(-2.5~{\rm kW}-1.25~{\rm kW}~1.25~{\rm kW}~2.5~{\rm kW})$ , is still high:  $\overline{\eta}_{\rm subopt}=93.1\%$ .

#### VIII. CONCLUSION

The paper presented here describes a general method to determine efficiency-optimal control parameters for a bidirectional DAB dc/dc converter. The resulting control parameters, calculated for a specific automotive DAB converter with a low-voltage/high-current port are used to synthesize an efficiency-optimized suboptimal modulation scheme. The paper goes on to propose an efficiency-optimized design procedure in order to determine the optimal transformer turns ratio n and the optimal DAB converter inductance L for a given converter setup.