## Approaches to Overcome the Google/@IEEE Little-Box Challenges

#### Johann W. Kolar et al.

ETH Zurich, Switzerland Power Electronic Systems Laboratory www.pes.ee.ethz.ch

#### Approaches to Overcome the Google/ IEEE Little-Box Challenges

#### All Team Members of ETH Zurich/Fraunhofer/Fraza

ETH Zurich, Switzerland Power Electronic Systems Laboratory www.pes.ee.ethz.ch

## **Outline**

- The Google Little Box Challenge

Selection of Converter Topology / Modulation Scheme

Components / Building Blocks

3D-CAD Construction

- Experimental Results

Conclusions

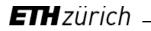

## The Google Little Box Challenge

Requirements Grand Prize Team \_\_\_\_\_

Google **IEEE**

- Design / Build the 2kW 1-OSolar Inverter with the Highest Power Density in the World

- Power Density > 3kW/dm<sup>3</sup> (50W/in<sup>3</sup>)

- Efficiency > 95%

- Case Temp. < 60°C

- EMI FCC Part 15 B

Push the Forefront of New Technologies in R&D of High Power Density Inverters

Google | �IEEE

- Design / Build the 2kW 1-OSolar Inverter with the Highest Power Density in the World

Power Density > 3kW/dm<sup>3</sup> (50W/in<sup>3</sup>)

- Efficiency > 95%

- Case Temp. < 60°C

- EMI FCC Part 15 B

■ Push the Forefront of New Technologies in R&D of High Power Density Inverters

# The Grand Prize

- Highest Power Density (> 50W/in<sup>3</sup>)

Highest Level of Innovation

■ Timeline

**ETH** zürich

- Challenge Announced in Summer 2014

- 650 Teams Worldwide

- 100+ Teams Submitted a Technical Description until July 22, 2015

- 18 Finalists / Presentation @ NREL on Oct. 21, 2015, Golden, Colorado, USA

Testing @ NREL, Colorado, USA / Winner will be Announced in Early 2016

## Multi-National Team

- Switzerland

- Germany Slovenia

Acknowledgment

ETH zürich \_\_\_\_\_

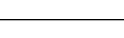

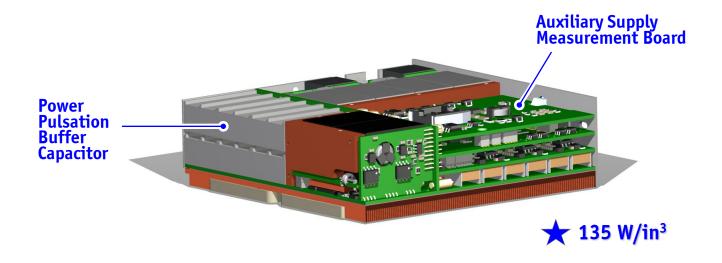

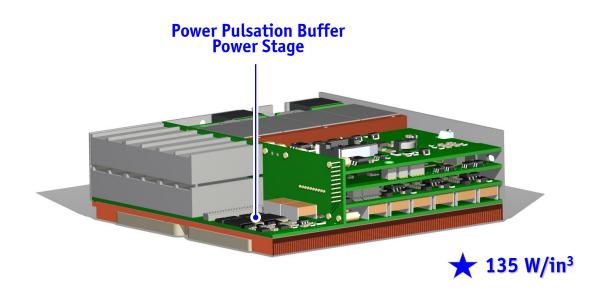

— 1- Power Pulsation Buffer —

# Power Pulsation Buffer (1)

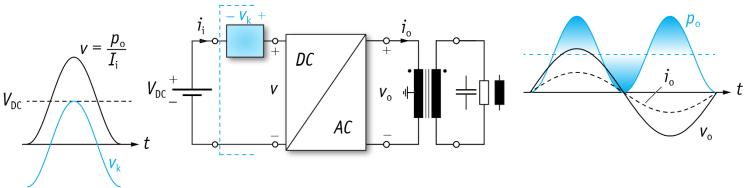

• Parallel Buffer @ DC Input

• Series Buffer @ DC Input

Parallel Approach for Limiting Voltage Stress on Converter Stage Semiconductors

## Power Pulsation Buffer (2)

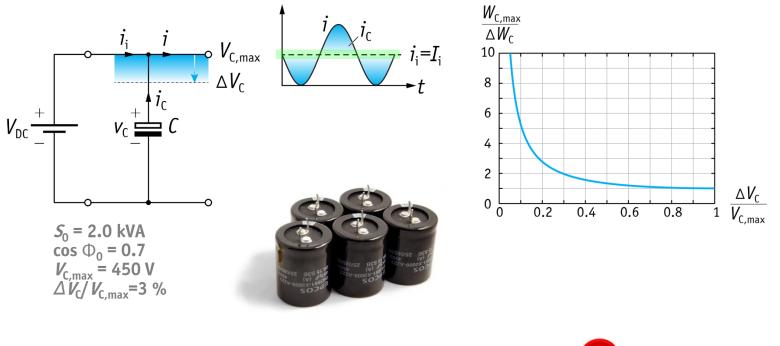

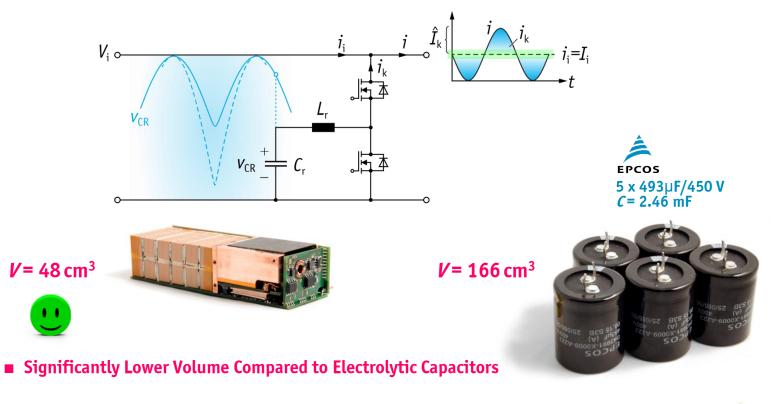

• Electrolytic Capacitor

**C** > 2.2mF / 166 cm<sup>3</sup>  $\rightarrow$  Consumes 1/4 of Allowed Total Volume !

## **Power Pulsation Buffer (3)**

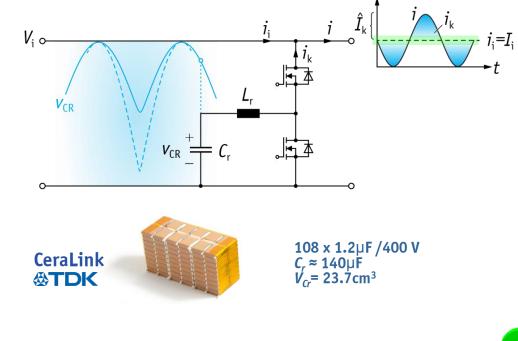

• Series Resonant Circuit / Used in Rectifier Input Stage of Locomotives

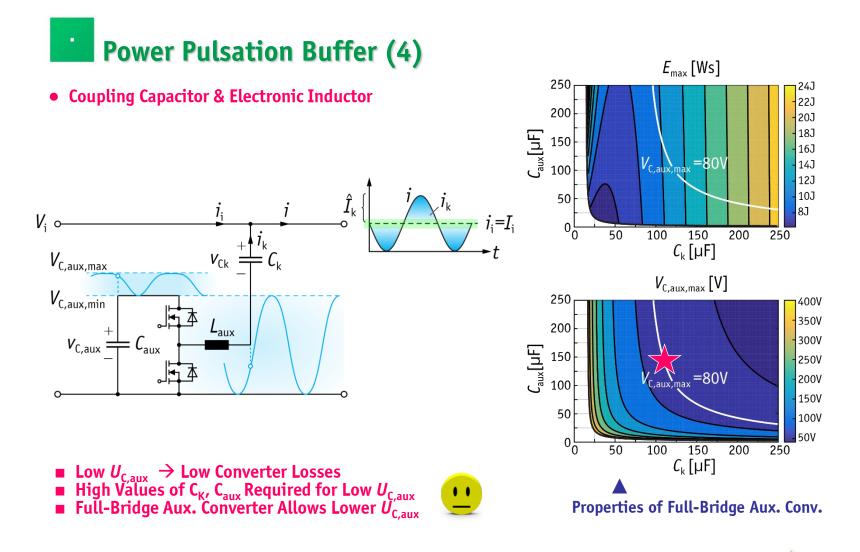

#### Power Pulsation Buffer (4-a)

- Large Voltage Fluctuation Capacitor & DC/DC Buck (Boost) Converter Stage

- Foil or Ceramic Capacitor

• Very Good Compromise  $\rightarrow$  C<sub>r</sub> - Volume / Power Electronics Complexity

## Power Pulsation Buffer (4-b)

- Large Voltage Fluctuation Capacitor & DC/DC Buck (Boost) Converter Stage

- Foil or Ceramic Capacitor

Output Stage —— Topology / Modulation ——

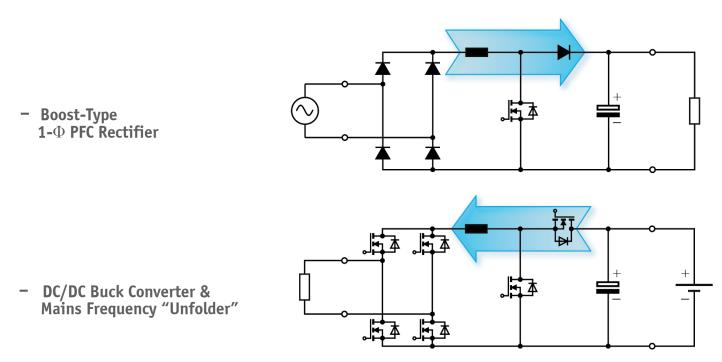

## Derivation of Output Stage Topology (1)

• Inversion of Basic 1- $\oplus$  PFC Rectifier Topology

Low-Frequency "Folder/ Unfolder" vs. PWM Operation of Output Stage

### Derivation of Output Stage Topology (2)

• DC/DC Buck Converter & Output Frequency "Unfolder"

PWM Operation of Mains Frequency Inverter @ U < U<sub>min</sub>

CM Component of Generated Output Voltage

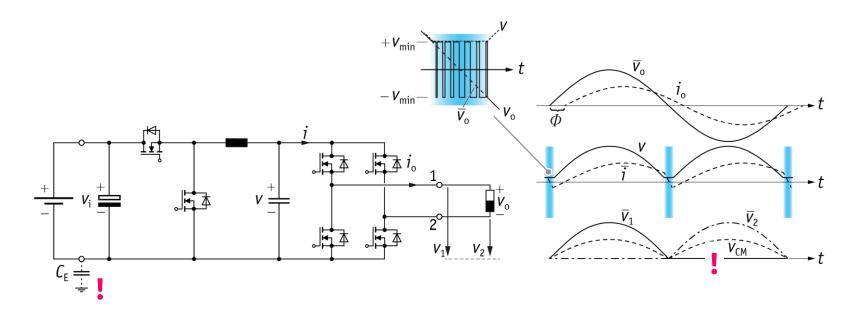

#### Derivation of Output Stage Topology (3)

• Full Bridge Output Stage / Output Frequency Bridge Leg

PWM Operation of Mains Freq. Bridge Leg @ |u| < u<sub>0,min</sub>

CM Component u<sub>CM</sub> of Generated Output Voltage

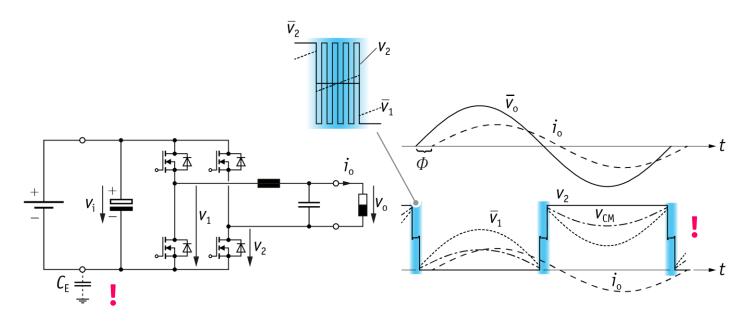

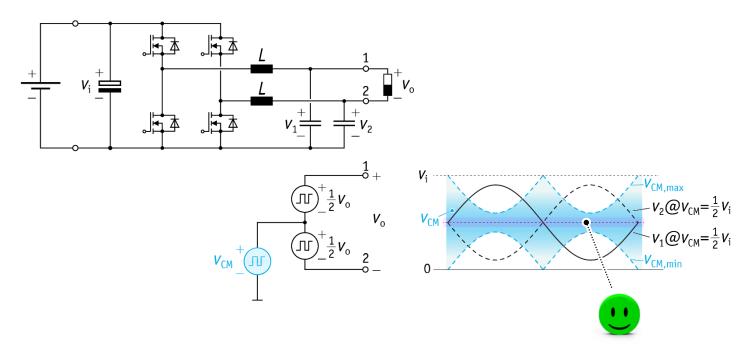

#### **Derivation of Output Stage Topology (4)**

• Full Bridge Output Stage / Full PWM Operation

- DM Component of  $u_1$  and  $u_2$  Defines Output  $u_0$ CM Component of  $u_1$  and  $u_2$  Represents Degree of Freedom of the Modulation (!)

#### **Remark:** AC Side Power Pulsation Buffer

• Full Bridge Output Stage / Full PWM Operation

- CM Reactive Power of Output Filter Capacitors used for Comp. of Load Power Pulsation

- CM Reactive Power prop. 2 C DM Reactive Power prop. 1/2 C

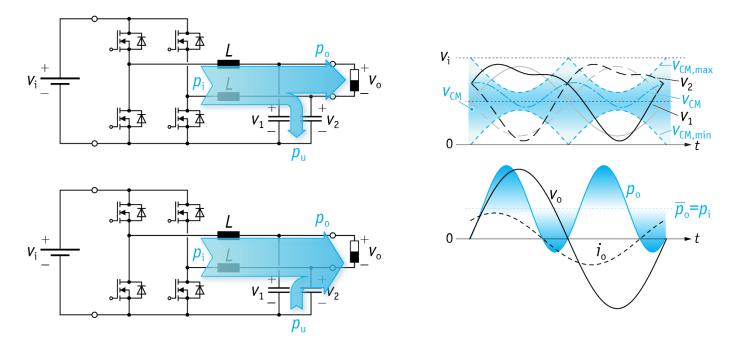

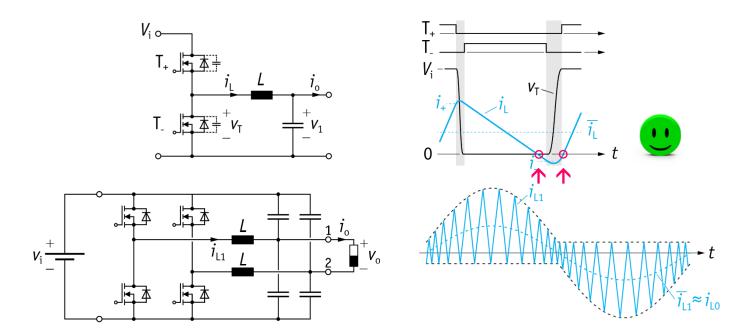

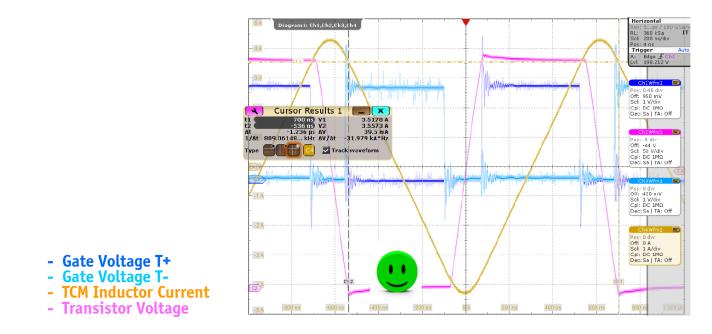

## ZVS of Output Stage / TCM Operation

• Full Bridge Output Stage / Full PWM Operation

- Triangular Current Mode (TCM) Operation for Res. Voltage Transition @ Turn-On/Turn-Off Required Only Measurement of Current Zero Crossings, *i* = 0

- Variable Switching Frequency Lowers EMI

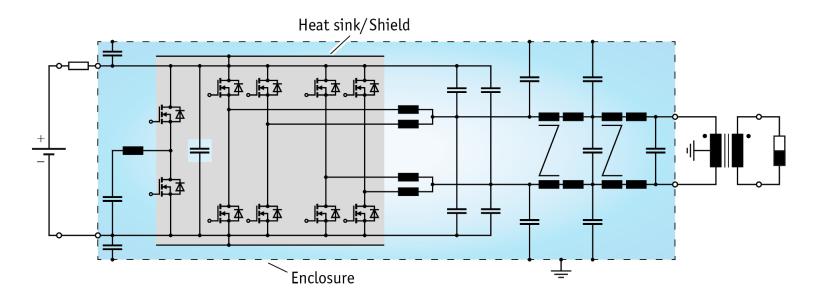

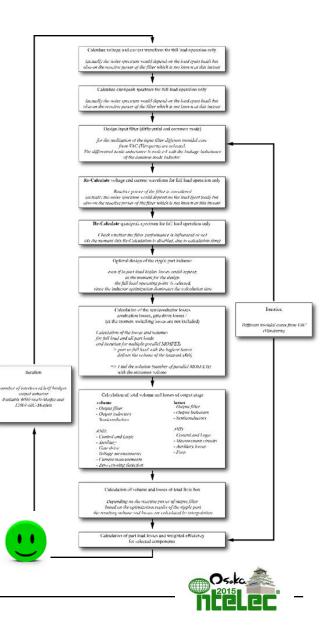

## Selected Converter Topology

- Interleaving of 2 Bridge Legs per Phase Volume / Filtering / Efficiency Optimum

- Active 1-O Output Power Pulsation Buffer

- ZVS of All Bridge Legs @ Turn-On/Turn-Off in Whole Operating Range 4D TCM Interleaving

Heatsinks Connected to DC bus / Shield to Prevent Capacitive Coupling to Grounded Enclosure

Interleaving —— Switching Frequ. Modulation —

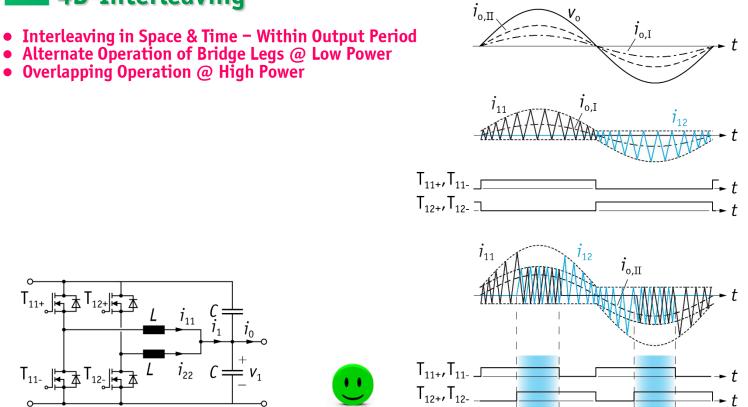

#### **4D-Interleaving**

- Overlapping Operation @ High Power

• Opt. Trade-Off of Conduction vs. Switching Losses / Opt. Balancing of Thermal Stress

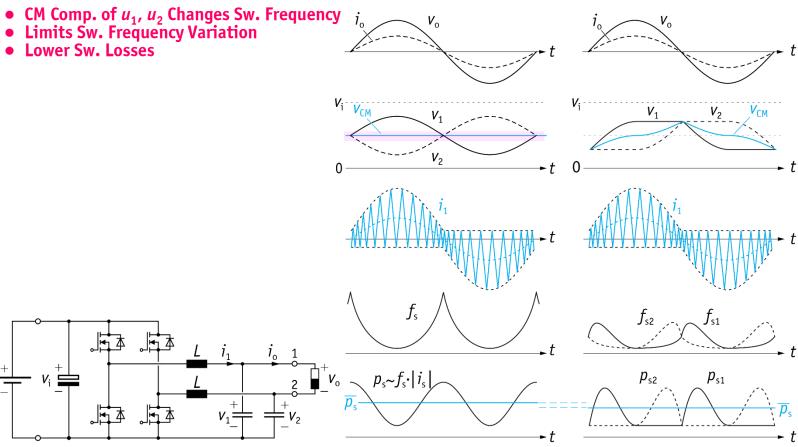

#### **Remark: CM-Enhanced TCM Modulation**

**ETH** zürich

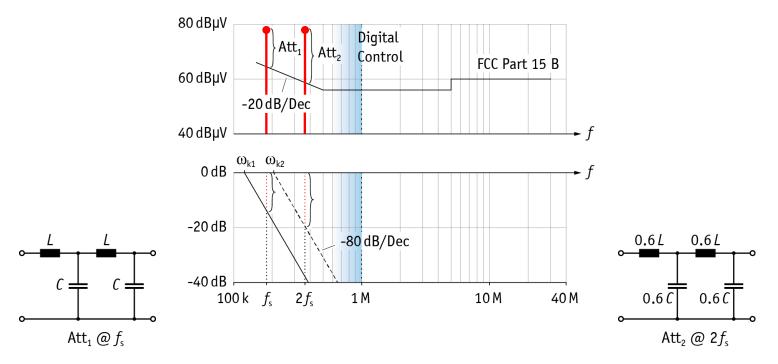

#### **Selection of Switching Frequency**

• Significant Reduction in EMI Filter Volume for Increasing Sw. Frequency

- Doubling Sw. Fequ. *f*<sub>s</sub> Cuts Filter Volume in Half Upper Limit due to Digital Signal Processing Delays / Inductor & Sw. Losses Heatsink Volume

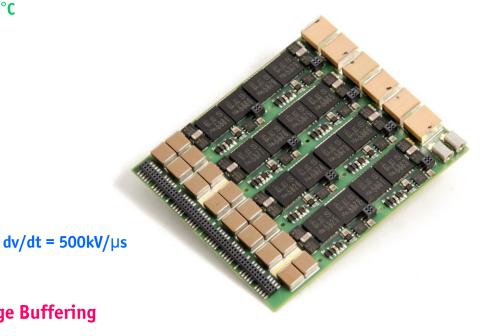

- 600V IFX Normally-Off GaN GIT ThinPAK8x8

2 Parallel Transistors / Switch

- Antiparallel CREE SiC Schottky Diodes

- 1.2V typ. Gate Threshold Voltage 55 m $\Omega$   $R_{DS,on}$  @ 25°C, 120m $\Omega$  @ 150°C 5 $\Omega$  Internal Gate Resistance

#### CeraLink Capacitors for DC Voltage Buffering

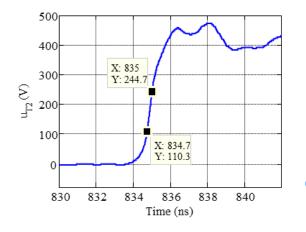

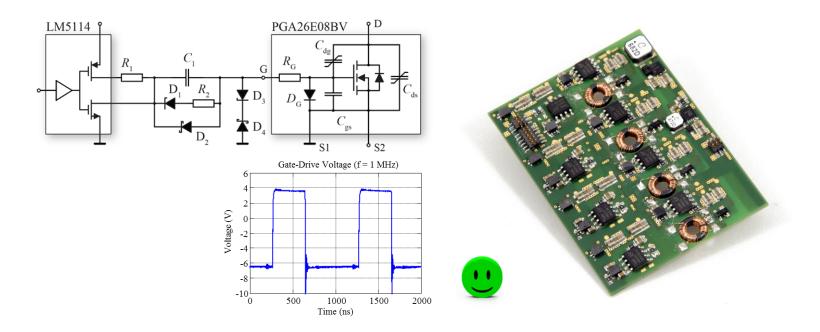

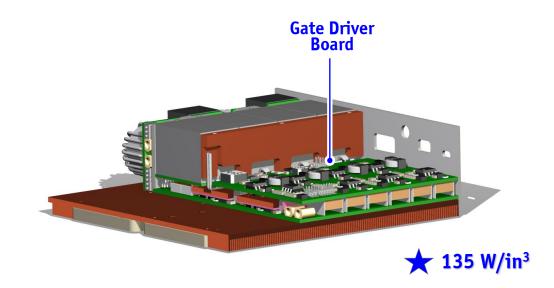

## Advanced Gate Drive

- Fixed Negative Turn-off Gate Voltage Independent of Sw. Frequency and Duty Cycle

- Extreme dv/dt Immunity (500 kV/µs) Due to CM Choke at Signal Isolator Input

Total Prop. Delay < 30ns incl. Signal Isolator, Gate Drive, and Switch Turn-On Delay

## · Advanced Gate Drive

- Fixed Negative Turn-off Gate Voltage Independent of Sw. Frequency and Duty Cycle

- Extreme dv/dt Immunity (500 kV/µs) Due to CM Choke at Signal Isolator Input

• Triangular Current Mode (TCM) Operation at No Load  $\rightarrow$  ZVS and No Free Ringing of  $u_{T+}$ ,  $u_{T-}$  or  $i_{L}$

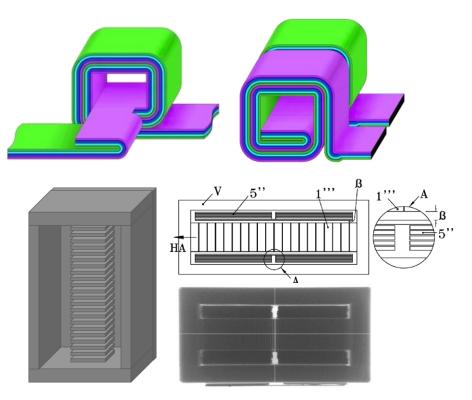

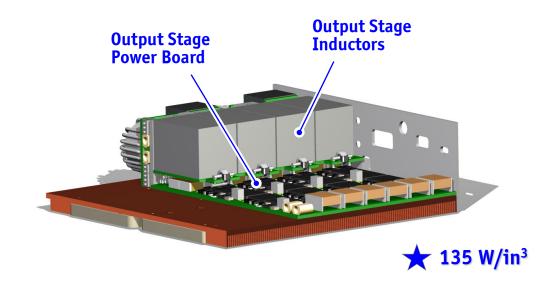

## **High Frequency Inductors**

- Multi-Airgap Inductor with Patented Multi-Layer Foil Winding Arrangement Minim. Prox. Effect

- Very High Filling Factor / Low High Frequency Losses Magnetically Shielded Construction Minimizing EMI

- Intellectual Property of F. Zajc / Fraza

- L= 10.5µH

- 2 x 8 Turns

**ETH** zürich

- 24 x 80µm Airgaps

Core Material DMR 51 / Hengdian

0.61mm Thick Stacked Plates

- 20 μm Copper Foil / 4 in Parallel

7 μm Kapton Layer Isolation

20mΩ Winding Resistance / Q=800

Terminals in No-Leakage Flux Area

Dimensions - 14.5 x 14.5 x 22mm<sup>3</sup>

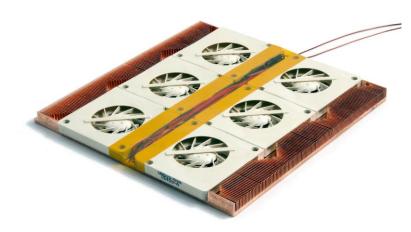

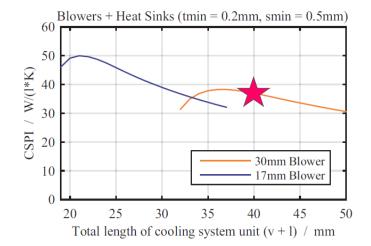

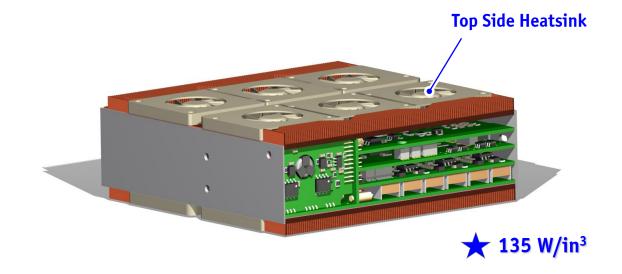

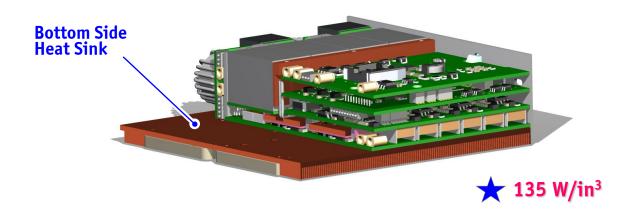

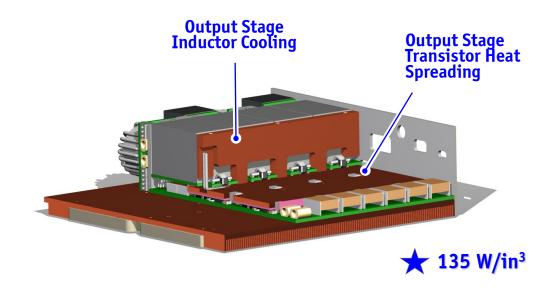

## **Thermal Management**

- 30mm Blowers with Axial Air Intake / Radial Outlet Full Optimization of the Heatsink Parameters

- •

- **Outstanding Cooling Syst. Performance Index**

- 200um Fin Thickness

- 500um Fin Spacing

3mm Fin Height

10mm Fin Length

CSPI = 37 W/(dm<sup>3</sup>.K)

1.5mm Baseplate

- 30mm Blowers with Axial Air Intake / Radial Outlet Full Optimization of the Heatsink Parameters Outstanding Cooling Syst. Performance Index

- •

**Two-Side Cooling**  $\rightarrow$  Heatsink Temperature = 52°C @ 80W (8W Natural Convection)

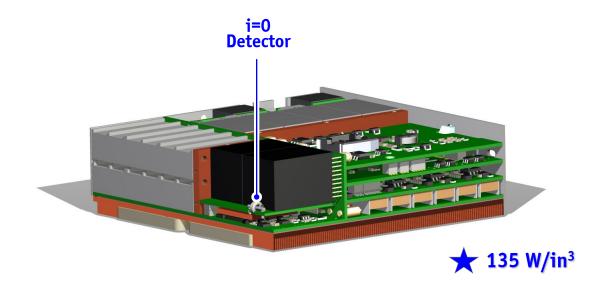

#### **Control Board & i=O Detection**

- Fully Digital Control Overall Control Sampling Frequency of 25kHz

- TI DSC TMS320F28335 / 150MHz / 179-pin BGA / 12mmx12mm Lattice FPGA LFXP2-5E / 200MHz / 86-pin BGA / 8mmx8mm

- TCM Current / Induced Voltage / Comparator Output

i=0 Detection of TCM Currents Using R4/N30 Saturable Inductors

Galv. Isolated / Operates up to 2.5MHz Switching Frequency / <10ns Delay</li>

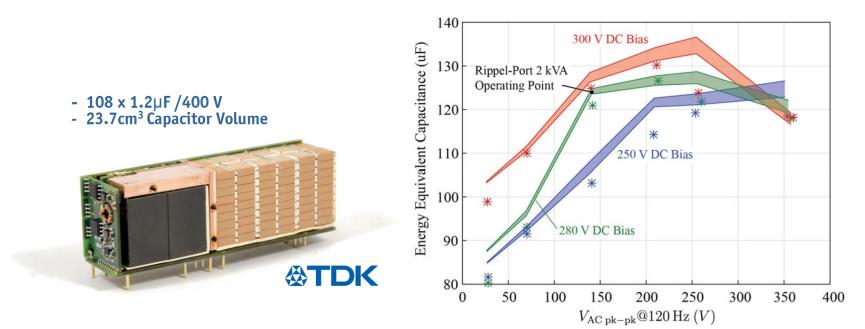

# Power Pulsation Buffer Capacitor

- High Energy Density 2<sup>nd</sup> Gen. 400VDC CeraLink Capacitors Utilized as Energy Storage

- Highly Non-Linear Behavior  $\rightarrow$  Opt. DC Bias Voltage of 280VDC

- Losses of 6W @ 2kVA Output Power

■ Effective Large Signal Capacitance of C ≈140µF

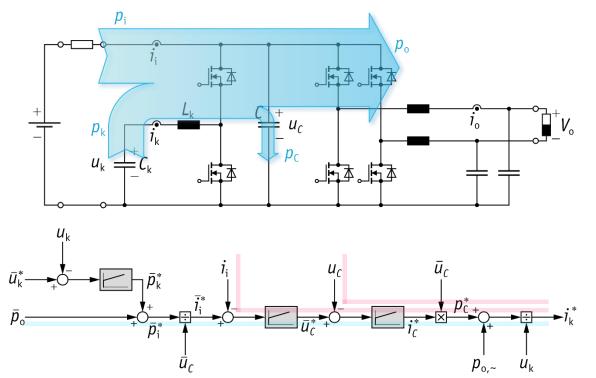

# Control of Power Pulsation Buffer

• Cascaded Control Structure

- Feedforward of Output Power Fluctuation

- Underlying Input Current / DC Link Voltage Control

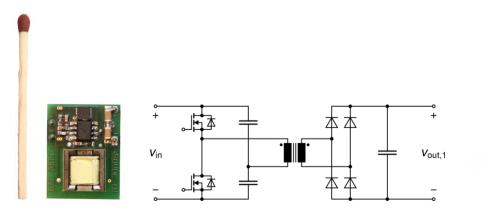

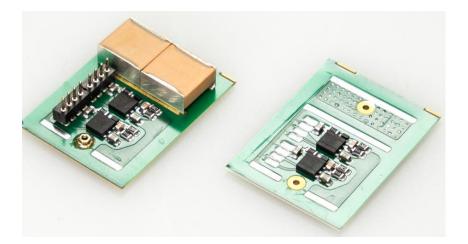

#### Auxiliary Supply & Measurements

- ZVS Constant 50% Duty Cycle Half Bridge with Synchr. Rectification

- Compact / Efficient / Low EMI

- 10W Max. Output Power

380V...450V Input Operating Range

16V...16V DC Output in Full Inp. Voltage / Output Power Range

90% Efficiency @ P<sub>max</sub>

**ETH** zürich

19mm x 24mm x 4.5mm (2cm<sup>3</sup> Volume )

**ETH** zürich

40/69

**3D-CAD** Construction

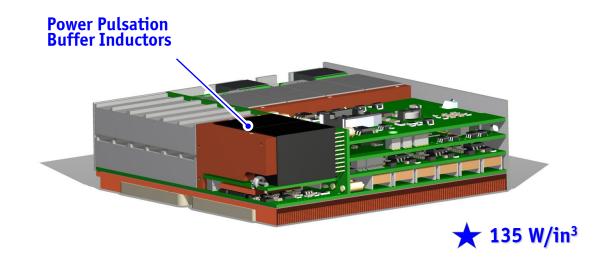

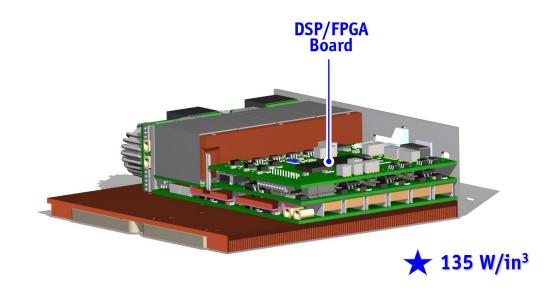

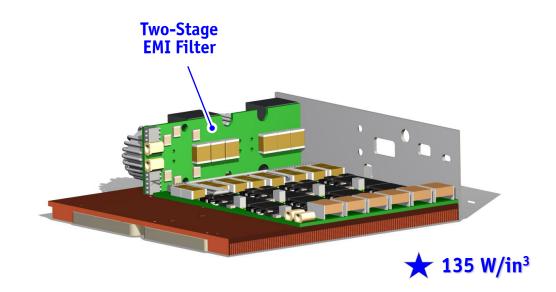

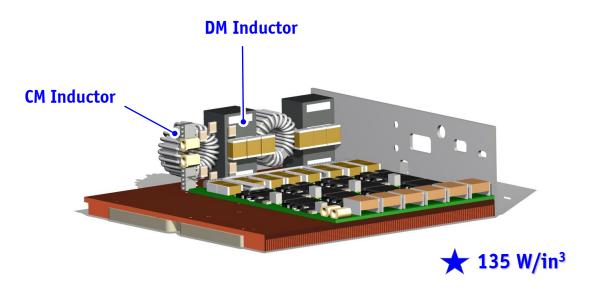

#### **3D-CAD Construction (10)**

• Built to the Power Density Limit @  $\eta$ = 95% /  $T_c$  < 60°C

# **3D-CAD Construction (13)**

• Built to the Power Density Limit @  $\eta$ = 95% /  $T_c$  < 60°C

#### **Experimental Results**

Hardware Output Voltage/Input Current Quality Thermal Behavior Efficiency EMI \_\_\_\_

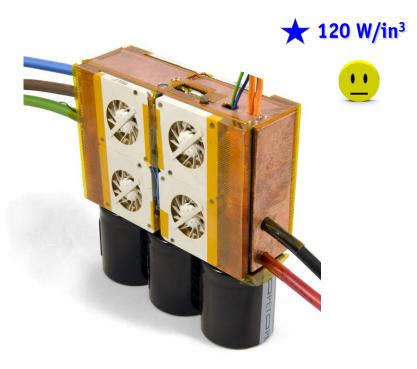

# Little-Box Prototype I

• System Employing Electrolytic Capacitors as  $1-\Phi$  Power Pulsation Buffer

273cm<sup>3</sup> 7.3 kW/dm<sup>3</sup> 97,5% Efficiency @ 2kW *T*<sub>c</sub>=58°C @ 2kW

$\Delta u_{\rm DC}$ = 2.85%  $\Delta i_{\rm DC}$ = 15.4% *THD*+N<sub>U</sub>= 2.6% *THD*+N<sub>I</sub>= 1.9%

97mm x 90.8 mm x 31mm (16.6in<sup>3</sup>)

Compliant to All Specifications

Osaka -

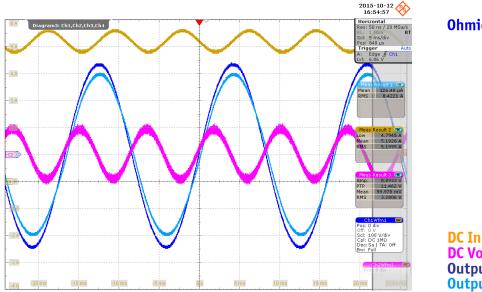

# Measurement Results I-(1)

• System Employing Electrolytic Capacitors as 1- $\Phi$  Power Pulsation Buffer

Ohmic Load / 2kW

DC Input Current DC Voltage Ripple Output Voltage Output Current

**Compliant to All Specifications**

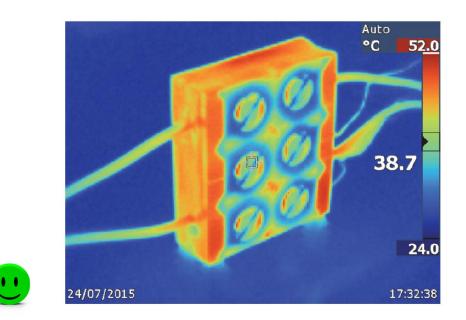

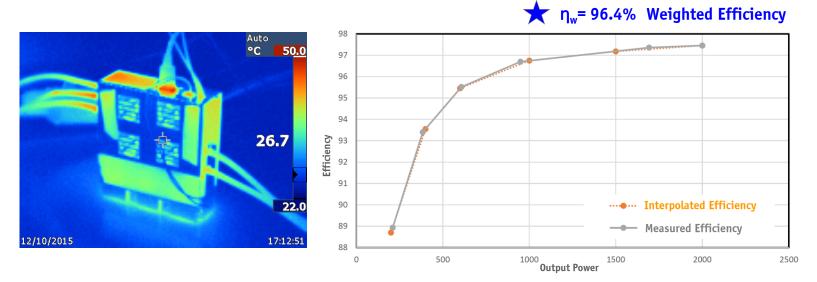

#### Measurement Results I-(2)

• System Employing Electrolytic Capacitors as 1- $\Phi$  Power Pulsation Buffer

■ Heating of System Lower than Specified Limit (*T*<sub>C,max</sub>= 60°C @ *T*<sub>amb</sub>= 30°C)

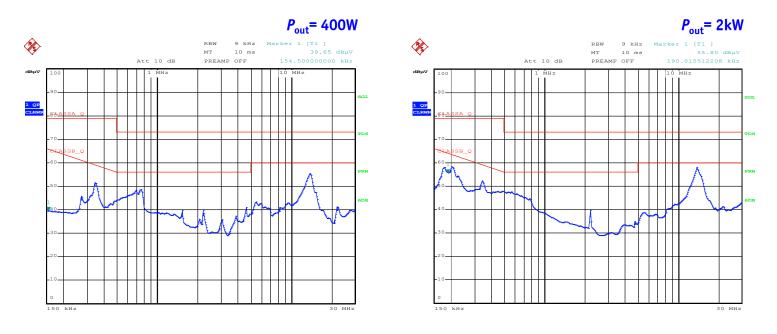

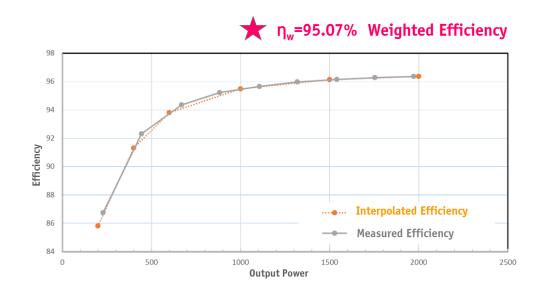

#### Measurement Results I-(3)

• System Employing Electrolytic Capacitors as 1- $\Phi$  Power Pulsation Buffer

• Compliant to All Specifications

**ETH** zürich

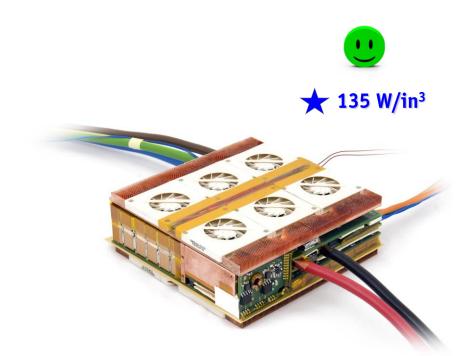

# Little-Box Prototype II-(1)

• System Employing Active 1-<sup>(1)</sup> Power Pulsation Buffer

243 cm<sup>3</sup> 8.2 kW/dm<sup>3</sup> 96,3% Efficiency @ 2kW  $T_c=58^{\circ}C$  @ 2kW  $\Delta u_{pc}=$  1.1%

$\Delta u_{\rm DC}$ = 1.1%  $\Delta i_{\rm DC}$ = 2.8% *THD*+N<sub>U</sub>= 2.6% *THD*+N<sub>I</sub>= 1.9%

88.7mm x 88.4mm x 31mm (14.8in<sup>3</sup>)

• Compliant to All Specifications

### Little-Box Prototype II-(1)

• System Employing Active 1-<sup>(1)</sup> Power Pulsation Buffer

243 cm<sup>3</sup> 8.2 kW/dm<sup>3</sup> 96,3% Efficiency @ 2kW  $T_c=58^{\circ}C$  @ 2kW  $\Delta u_{DC}=$  1.1%  $\Delta i_{DC}=$  2.8% THD+N<sub>U</sub>= 2.6% THD+N<sub>I</sub>= 1.9%

88.7mm x 88.4mm x 31mm (14.8in<sup>3</sup>)

• Compliant to All Specifications

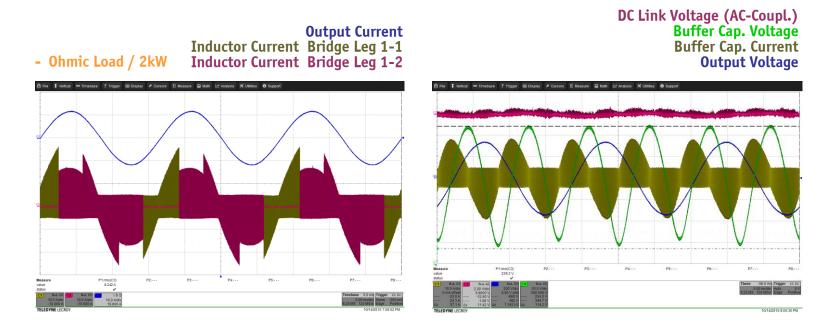

# Measurement Results II-(2)

• System Employing Active 1- $\Phi$  Power Pulsation Buffer

• Compliant to All Specifications

#### Measurement Results II-(3)

• System Employing Active 1- $\Phi$  Power Pulsation Buffer

• Compliant to All Specifications

**ETH** zürich

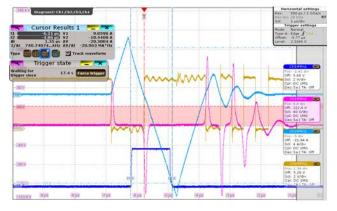

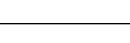

# Measurement Results II-(5)

• System Employing Active 1- $\Phi$  Power Pulsation Buffer

Start-up and Shut-Down (No Load Operation)

■ **Conclusions** \_\_\_\_

# · Conclusions

- 2kVA 1-① Inverter @ 240cm<sup>3</sup> (15in<sup>3</sup>)

- 400...450VDC Input / 240VAC<sub>rms</sub> Output

- Efficiency > 95%

- Case Temp. < 60°C

- EMI FCC Part 15 B

#### Lessons Learned

**ETH** zürich

- Upper Sw. Frequency Limit of ≈1MHz Due to Digital Control / i=0 Detection

- Integrated Gate Driver for Even Higher Power Density

- High Frequency Low Loss Magnetics are Key Issue

- Isol. Distance Requirements Difficult to Fulfill

- Losses of Ceramic Capacitors for Large AC Ripple

- Careful Mounting of Ceramic Caps.

- New U-I-Probes Required for Ultra-Compact Conv. R&D

- Convergence of Sim. & Measurem. Tools  $\rightarrow$  Next Gen. Oscilloscope

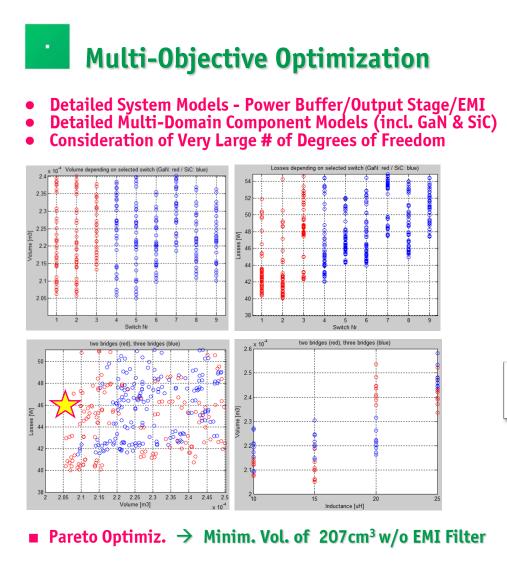

- New Multi-Obj. Multi-Domain Simulation/Optim. Tools

- Low Frequency (20kHz...120kHz) SiC vs. HF (200kHz...1.2MHz) GaN

$\rightarrow$  8kW/dm<sup>3</sup> (135W/in<sup>3</sup>)

- 100+ Teams

- 3 Members / Team, 1 Year

- 300 Man-Years

- 3300 USD / Man-Year

- Embedded Switching Cell Package for Further Size Reduction

- Integr. Half Bridge Module incl. DC Link Caps and Drivers

- 2 Parallel Chips / SwitchEmbedded in PCB

**ETH** zürich

- 8 mm Smaller than Conv. Design

Extremely Low DC Link Indutance

Driver Directly on Top of Switches

Very Low Gate Inductance

# **Thank You!**