of autonomous, plug-and-play-type systems with minimal coordination in their power flow and energy management was foreseen.

The session concluded with a positive outlook of the ongoing changes that are currently transforming the grid and its capabilities. The attendees also acknowledged the multiple opportunities in new emerging regions to develop new power networks virtually from scratch, where the role of power electronics would be preponderant from the beginning.

### **About the Authors**

**Rolando Burgos** (roburgos@vt.edu) received his B.S., M.S., and Ph.D. degrees from the University of Concepción, Chile, in 1995, 1999, and 2002, respectively. He is a professor with the Center for Power Electronics Systems in the Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg.

*Jian Sun* (jsun@rpi.edu) received his B.S. degree in electrical engineering from the Nanjing University of Aeronautics and Astronautics, China, in 1984, his M.S. degree in electrical engineering from the Beijing University of Aeronautics and Astronautics in 1989, and his Ph.D. degree in electrical engineering from the University of Paderborn, Germany, in 1995. He is a professor in the Department of Electrical, Computer, and Systems Engineering, Rensselaer Polytechnic Institute (RPI), Troy, New York. He is also the director of the New York State Center for Future Energy Systems, RPI.

# Power Electronics Design Methods and Automation in the Digital Era

# Evolution of design automation tools

by Antonio J. Marques Cardoso

ast June at the 10th IEEE Future of Electronic Power Processing and Conversion (FEPPCON X) workshop, I chaired the session "Power Electronics Design Methods and Automation in the Era of Digitalization," which was held 26 June 2019 at

Digital Object Identifier 10.1109/MPEL.2020.2988077 Date of current version: 16 June 2020 Scandic Ishavshotel in Tromso, Norway. To foresee the evolution of design automation tools in the power systems arena, this session offered presentations from two distinguished speakers, Prof. Alan Mantooth from the University of Arkansas, Fayetteville, and Prof. Johann W. Kolar from ETH Zurich, Switzerland.

In his presentation "Power Electronics Design Methods and Automation in the Era of Digitalization," Prof. Mantooth

#### 36 IEEE POWER ELECTRONICS MAGAZINE 🛛 June 2020

Authorized licensed use limited to: ETH BIBLIOTHEK ZURICH. Downloaded on July 20,2020 at 15:39:22 UTC from IEEE Xplore. Restrictions apply.

initiated the session by anticipating the following potentially controversial conclusions:

- power electronics design is lacking in automation

- current approaches limit penetration

- Power Electronics Design 4.0 demands a change in the IEEE Power Electronics Society (PELS) composition.

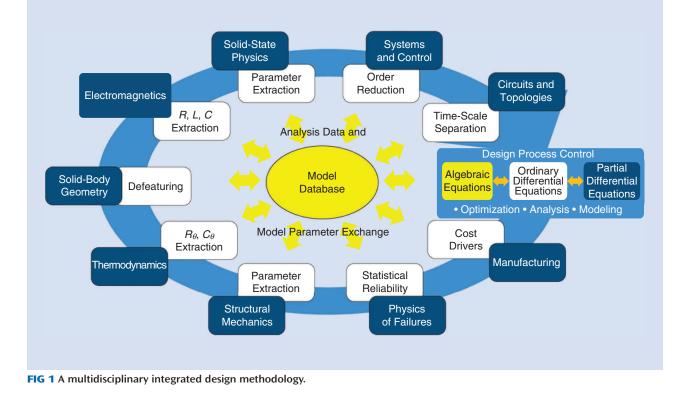

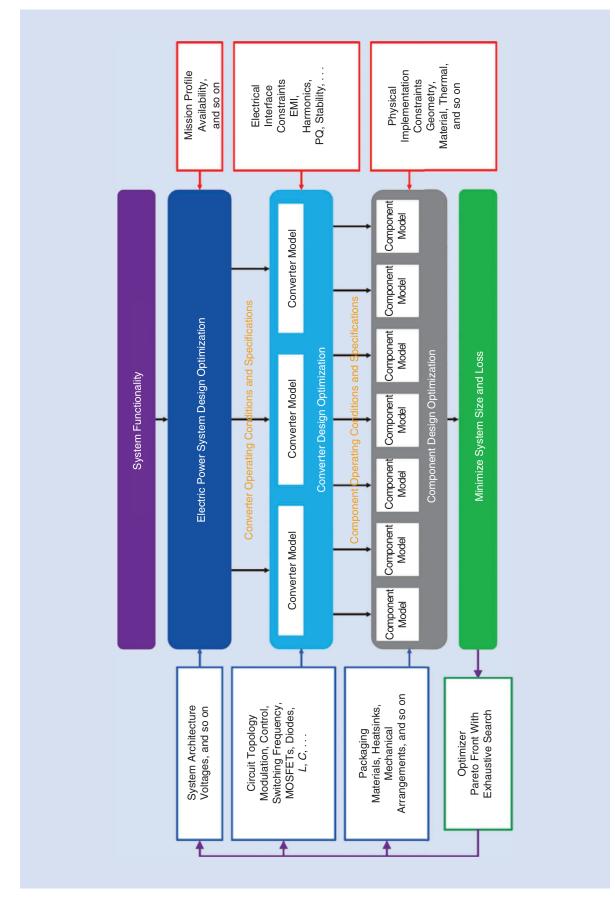

Subsequently, Prof. Mantooth presented some evidence to support his initial claims: the multidis-

ciplinary integrated design methodology (Figure 1) and the multidisciplinary hierarchical optimization design flowchart (Figure 2). These illustrations highlighted key bottlenecks limiting automation in power systems, such as the difficulties of combining systemlevel with component-level designs, the absence of industry interchangeable models, the lack of software standards, and the need for better algorithms and open source libraries.

Prof. Mantooth continued by stating that what limits penetration is not just nominal design, but robustness, resiliency, and reliability. Although certain applications with specific voltage/current/power specifications may first see the penetration of automated design tools, the key barrier to design automation seems to be the device data sheets, which are not a true representation of the device's

Prof. Mantooth continued by stating that what limits penetration is not just nominal design, but robustness, resiliency, and reliability. performance. In reality, the current situation demands more automation, concluded Prof. Mantooth.

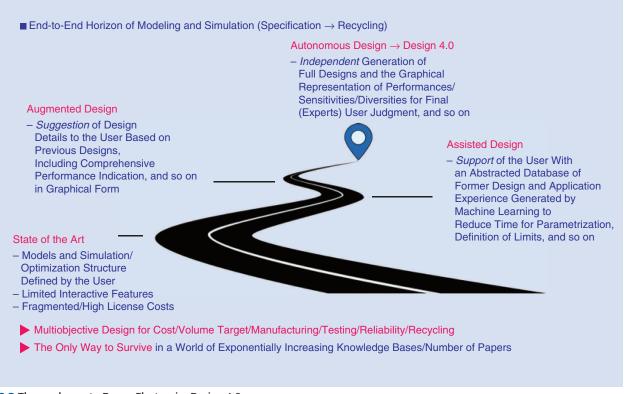

Also, based on the road map to Power Electronics Design 4.0 (Figure 3), Prof. Mantooth questioned the current PELS composition to achieve the road map's demanding targets. He would like to see a PELS initiative, comprising the right folks, to drive this road map in the future.

Continuing, Prof. Mantooth presented the second Design Automation for Power Electronics workshop,

which was held on 6 September 2019 at the same venue as that of the PELS-sponsored European Conference on Power Electronics and Applications at the Magazzini del Cotone Conference Center in Genova, Italy. The intent here was to understand the problems hindering the growth of design automation in power electronics and how best to address them. It brought together experts in both power electronics and design automation from the academia and industry, all of whom presented their perspectives on the emerging needs.

Finally, several illustrative examples taken from the Workshop on Wide Bandgap Power Devices and Applications Asia 2019 held in Taipei, Taiwan, regarding advances in silicon carbide power integrated circuits were presented and discussed, which included µ-cooled flip-chip modules and integrated CMOS gate drivers.

June 2020 💌 IEEE POWER ELECTRONICS MAGAZINE 37

Authorized licensed use limited to: ETH BIBLIOTHEK ZURICH. Downloaded on July 20,2020 at 15:39:22 UTC from IEEE Xplore. Restrictions apply.

#### 38 IEEE POWER ELECTRONICS MAGAZINE 📕 June 2020

#### **Peeking Into the Future**

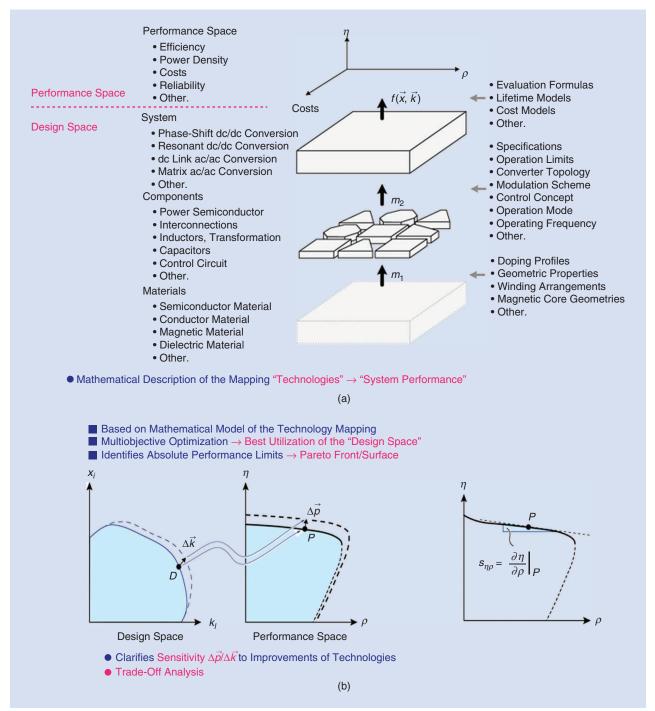

Prof. Kolar focused his presentation on the topics of automated design, digital twin, and Industry 4.0. Under the scope of automated design, he discussed the design and performance spaces [Figure 4(a) and (b)], showing the functions and parameters that divide the two. In fact, his talk suggested that automation can deliver the technologies needed to optimally map the design space into the performance space. In addition, he also introduced absolute performance limits, labeled as a Pareto front. Concurrently, Prof. Kolar also

Prof. Kolar's talk suggested that automation can deliver the technologies needed to optimally map the design space into the performance space.

introduced the concept of a digital twin, which means that for every physical device there is a digital mirror image.

Based on the aforementioned presentations and the involved discussion that ensued, the following general conclusions were drawn jointly by myself and Prof. Prasad Enjeti of Texas A&M University:

- Current power electronics design is lacking in automation, but it is not just nominal design, it is also missing the following characteristics:

- robustness (design centering and tolerancing, and uncertainty)

- resiliency (over environment and compromise)

- reliability.

- Automated design tools for certain applications with specific voltage/ current/power levels is probably the first set of applications.

- One of the key barriers to design automation seems to be that the device data sheets are not a true representation of the device's performance.

- Design automation can simplify the design of passive components, introduce sensitivity analysis, affect component tolerances on system performance, and so forth.

- Digital twin—physics-based digital mirror image. The digital replica of a physical asset such as a power electronic converter/system, which can merge live data from its physical counterpart using an interactive visual interface, has the potential to drastically enhance performance.

- Current approaches limit penetration.

- Power Electronics Design 4.0 demands a change in PELS composition.

- A second workshop on design automation has been organized. A new initiative on design automation in power electronics will probably have good traction.

FIG 3 The road map to Power Electronics Design 4.0.

**FIG 4** (a) The automated design maps plot space into performance and (b) identify its absolute performance limits, denoted as the Pareto front.

## **About the Author**

Antonio J. Marques Cardoso (ajmcardoso@ieee.org) received his Dipl. Eng., Dr. Eng., and habilitation degrees from the University of Coimbra, Portugal, in 1985, 1995, and 2008, respectively, all in electrical engineering. He is a full professor in the Department of Electromechanical Engi-

neering, at the University of Beira Interior (UBI), Covilhã, Portugal, and the director of the Electromechatronic Systems Research Centre at UBI. His current research interests are in fault diagnosis and fault tolerance in electrical machines, power electronics, and drives. He is a Senior Member of the IEEE.