© 2024 IEEE

IEEE Transactions on Power Electronics, Vol. 39, No. 11, pp. 14691-14707, November 2024

# Analytical Modeling and Comparison of EMI Pre-Filter Noise Emissions of Three-Phase Voltage and Current DC-Link Converters

D. Zhang,

M. Leibl,

J. Mühlethaler,

J. Huber,

J. W. Kolar

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works

# Analytical Modeling and Comparison of EMI Pre-Filter Noise Emissions of Three-Phase Voltage and Current DC-Link Converters

Daifei Zhang, Michael Leibl, Jonas Mühlethaler, Jonas Huber, and Johann W. Kolar

Abstract-Three-phase power-factor-correction (PFC) rectifiers o r m otor d rive i nverters c an b e r ealized u sing t wo dual converter topologies featuring either a voltage DC-link (voltage source) or a current DC-link (current source). This paper presents a generic comparison of the pre-filter differential-mode (DM) and common-mode (CM) electromagnetic interference (EMI) noise emissions of these two topologies (considering only the switching stage), which serve as indicators for the required EMI filter attenuation and, hence, EMI filter realization effort. In contrast to the voltage DC-link topology, the DM pre-filter noise of the current DC-link topology is primarily attributed to the current pulses generated by its switching stage, resulting in highfrequency voltage drops across the 50- $\Omega$  measurement resistor employed in line-impedance stabilization networks (LISNs) as defined by, e.g., the CISPR 11 standard. Addressing this aspect, low-complexity analytical expressions for approximating the envelopes of the pre-filter D M a nd C M n oise a mplitude spectra are derived and experimentally verified u sing 400 V (line-toline rms), 10 kW voltage and current DC-link AC/DC converter demonstrator systems. The DM pre-filter noise of current DC-link converters is lower than that of the voltage DC-link converters if the equivalent AC resistance the converter represents to the mains is higher than the LISN's 50- $\Omega$  measurement resistor. On the other hand, the current DC-link converter's CM pre-filter noise is, in typical cases, lower than the voltage DC-link converter's; current DC-link converters are thus an interesting choice for motor drive inverter applications.

#### I. INTRODUCTION

o ensure electromagnetic compatibility (EMC), all power electronic converter systems connected to the public lowvoltage mains must comply with specific limits for electromagnetic interference (EMI) noise emissions defined in standards such as CISPR 11 [1]. These limits are specified as a voltage across a 50- $\Omega$  measurement resistor  $R_{\rm m}$  that is part of a line impedance stabilization network (LISN), see Fig. 1a. The voltage limits are frequency-dependent (150 kHz to 30 MHz today [1]; future extensions down to 2 kHz are in preparation [2]) and typically in the range of  $0.2\,\mathrm{mV}$  to  $10\,\mathrm{mV}$  ( $46\,\mathrm{dB}\mu\mathrm{V}$ to 80 dBµV). Power converters achieve compliance with EMI limits by employing one or more LC filter stages to attenuate the pre-filter noise generated by the switching stage [3]–[7], whereby separate filter stages for differential-mode (DM) and common-mode (CM) noise components are always implemented [8]–[10]. The required filter attenuation determines the EMI filter's size and losses. Thus, converter topologies with low pre-filter noise emission levels are preferred.

Three-phase  $(3-\Phi)$  pulse-width modulated (PWM) converters find a wide range of industrial applications, e.g., as EV chargers or PV inverters. There are two fundamental, dual

converter topologies [11], [12]. For both, i.e., for voltage DC-link (voltage source) converters [13], [14] and current DC-link (current source) converters [15], [16], extensive research has been conducted on modeling the DM and CM EMI noise sources and designing the corresponding EMI filters, e.g., the required attenuation of the EMI filter is conventionally determined using circuit simulations [17]–[19]. Comparisons of DM and CM EMI filtering efforts between voltage and current DC-link converters have also been presented for several specific realizations [20]–[23].

However, a generic comparison of the DM and CM EMI filter attenuation requirements for voltage and current DC-link converters is still missing. Such a generic comparison should be based on modeling the DM and CM noise sources using straightforward analytic expressions. Whereas [24] provides a suitable simplified modeling procedure for the DM emissions of single-phase voltage DC-link systems, a similar approach for  $3-\Phi$  systems remains absent.

Therefore, in this paper, the method from [24] is first extended to model the pre-filter DM and CM noise emissions of 3-Φ voltage DC-link (Section II) and current DC -link converters (Section III). The resulting low-complexity analytic approximations of the DM and CM pre-filter noise emission amplitude spectra capture the characteristic dependencies on the mains voltage and output power level and/or DC-link voltage and DC-link current. Second, these analytical approximations facilitate a generic comparison of the DM and CM EMI filter attenuation requirements of voltage and current DClink converters in **Section IV**. Depending on the equivalent AC resistance the converter represents to the mains in relation to the LISN measurement resistance, either voltage or current DC-link rectifiers result in lower pre-filter DM EMI noise emissions and, therefore, require less filter attenuation. On the other hand, the pre-filter CM noise emissions of current DClink converters tend to be lower for most typical voltage and power levels, which is especially advantageous for motor drive inverter applications. Finally, **Section V** concludes the paper.

# II. EMI Pre-Filter Noise Emission of Three-Phase Voltage DC-Link PFC Rectifier Systems

The two-level 3- $\Phi$  voltage DC-link PFC rectifier (see **Fig. 1a**) is a widely used industry-standard solution due to its simplicity and reliability. Depending on the 3- $\Phi$  switching

<sup>1</sup>For the sake of clarity, the paper considers PFC rectifiers for the explanations. Nevertheless, the derived expressions for the DM and CM pre-filter noise emissions and the conclusions are also valid for the opposite power flow direction of, e.g., PV inverter or motor drive inverter systems.

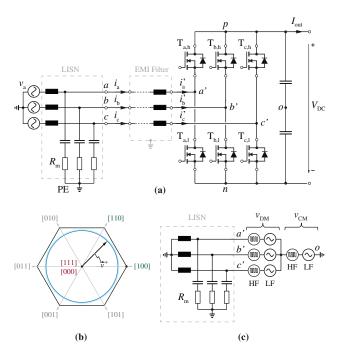

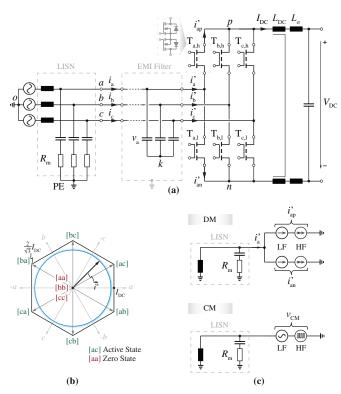

Fig. 1: (a) Power circuit of a two-level three-phase  $(3-\Phi)$  voltage DC-link PFC rectifier (including an EMI filter stage where boost inductors are shown as the first filtering components) connected to the mains via a LISN. (b) The rectifier's switching stage can generate six active and two zero voltage space vectors (SVs) at the switching nodes; SVPWM is typically used to synthesize a desired local average voltage SV  $\vec{v}^*$ . (c) Combined DM and CM equivalent circuit where the switching stage is modeled by DM and CM voltage sources (both LF and HF); the HF DM and CM voltage sources represent the DM and CM pre-filter noise emissions.

state, typically formed by three two-level bridge legs, a total of six active and two zero voltage space vectors (SVs) shown in **Fig. 1b** can be generated at the input of the switching stage. During each switching period, a local average voltage SV  $\vec{v}^*$  is generated, corresponding to three local average values of the  $3\text{-}\Phi$  voltages. This is achieved by applying each adjacent voltage SV during its respective dwell time. Typically, the correct sequence and dwell times are obtained using SV pulsewidth modulation (SVPWM), which is further explained in **Appendix A**.

Furthermore, the pre-filter DM and CM EMI noise emissions can be modeled by replacing the switching stage with three voltage sources that represent the switch-node phase voltages with respect to the (virtual) midpoint o of the DC output, i.e.,  $v_{a'o}$ ,  $v_{b'o}$ , and  $v_{c'o}$ . These voltage sources can then be decomposed into dedicated voltage sources for lowfrequency (LF) DM and CM components (e.g., the desired synthesized DM input voltage) as well as high-frequency (HF) DM and CM noise voltage sources (see Fig. 1c). This facilitates a decoupled analysis of DM and CM pre-filter noise emissions and, ultimately, of the filter designs. Note that the direct connection of the DC-link midpoint to protective earth (PE) shown in **Fig. 1c** represents the worst case for CM noise. This worst case for CM noise emissions is ensured by shorting the parasitic capacitances, which would be in series with the LISN measurement resistors as voltage dividers, and by disconnecting the capacitances, which would be connected in parallel to the LISN measurement resistors as current shunts.

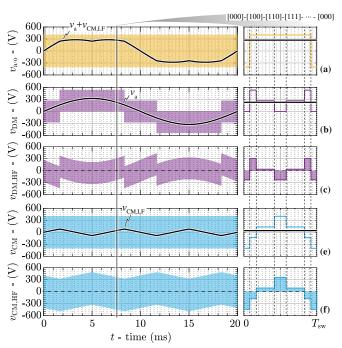

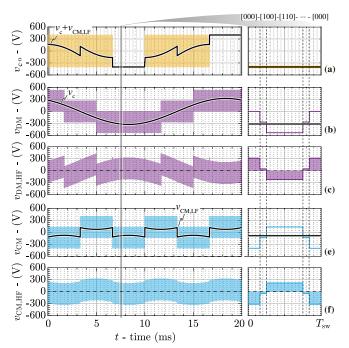

Fig. 2: Simulated key waveforms (with a zoomed view over one switching period) of the two-level 3- $\Phi$  voltage DC-link PFC rectifier (see Fig. 1a) operating with a 400 V (line-to-line rms) mains, 800 V DC-link and/or output voltage, and 10 kW output power using the standard SVPWM. Taking phase a as an example, (a) shows the switching stage phase voltage  $v_{a'o}$ , which can be decomposed into (b) DM and (e) CM components. Furthermore, (c) and (f) show the DM and CM HF noise voltages (i.e., the pre-filter DM and CM noise emissions). Note that a typical symmetric switching sequence, i.e., mirrored with respect to the center of a switching period or the switching state [111] in the selected sector, is applied, and only the first half over one switching period is shown on top.

Both effects would result in reduced CM noise emissions. <sup>2</sup>

Taking phase a of the analyzed two-level  $3-\Phi$  voltage DC-Link PFC rectifier as an example, the DM and CM voltage sources are expressed as [13], [14]:

$$v_{\rm DM} = v_{\rm DM,LF} + v_{\rm DM,HF} = v_{\rm a'o} - v_{\rm CM}, \tag{1}$$

$$v_{\rm CM} = v_{\rm CM,LF} + v_{\rm CM,HF} = \frac{1}{3} \cdot (v_{\rm a'o} + v_{\rm b'o} + v_{\rm c'o}).$$

(2)

Fig. 2 shows simulated key waveforms of these LF and HF DM and CM voltages.

### A. Analytical DM and CM Pre-Filter Noise Envelopes

Aiming for a generic comparison of the pre-filter noise emissions of voltage and current DC-link converters, low-complexity expressions that characterize the respective noise spectra are needed. Reference [24] has proposed a method for estimating the DM noise by concentrating the entire DM HF noise energy (i.e., the total HF rms noise voltage) in a single harmonic at the switching frequency,  $f_{\rm sw}$ , and then assuming an envelope with a decay of  $-20\,{\rm dB/dec}$  for  $f>f_{\rm sw}$ , see

<sup>&</sup>lt;sup>2</sup>The parasitic capacitances (transistors' drain tabs to the heat sink, DC bus rails to housings, etc.) at the DC rails *p* and *n* are shorted; otherwise, these parasitic capacitors and the LISN measurement resistors would form a frequency-dependent voltage divider and result in reduced CM noise emissions. Also, the parasitic capacitances (transistors' drain tabs to the heat sink) at the AC terminals *a'*, *b'* and *c'* are assumed to be open-circuit to eliminate possible frequency-dependent current shunt paths.

Fig. 3: (a) Typical rms spectrum of a switched voltage waveform including an LF fundamental component ( frequency  $f_{\rm m}$ )  $V_{\rm LF,rms}$  and HF harmonics  $V_{\rm HF,rms}$  at integer multiples of the switching frequency (side bands). (b) Simplified noise estimation method presented in [24] for single-phase converters: all HF rms noise energy is concentrated in a lumped/single harmonic  $V_{\rm HF,rms}$  at the switching frequency  $f_{\rm sw}$  and an envelope with a slope of  $-20~{\rm dB/dec}$  is used for estimating noise levels for  $f > f_{\rm sw}$ .

**Fig. 3**. Whereas reference [24] finds adequate accuracy when predicting DM quasi-peak (QP) emissions, we show a very good match between the simplified envelope and the amplitude spectra of the pre-filter DM and CM noise for voltage DC-link converters and, later, current DC-link converters (see **Section III**); this, in any case, is sufficient for the intended comparative analysis of the DM and CM pre-filter noise emissions generated by voltage and current DC-link systems.

The simplified analytical DM and CM noise envelopes are based on the rms values of the HF DM and CM noise voltages (see  $v_{\rm DM,HF}$  and  $v_{\rm CM,HF}$  in **Fig. 2c** and **Fig. 2f**). Therefore, analytic expressions are derived in the following. Again, taking phase a as an example,  $v_{\rm a'o}$  (see **Fig. 2a**) is a rectangular switched voltage attaining the two levels  $+V_{\rm DC}/2$  and  $-V_{\rm DC}/2$ ; thus

$$V_{\text{a'o,rms}} = \frac{V_{\text{DC}}}{2},\tag{3}$$

which is independent of the modulation scheme and the modulation index. Out of the switched voltage  $v_{\rm a'o}$ , an LF (i.e., fundamental frequency of 50 Hz or 60 Hz for a PFC rectifier) DM sinusoidal phase voltage  $v_{\rm DM,LF}$  (see **Fig. 2b**) is generated to interface the 3- $\Phi$  mains with a rms value of

$$V_{\rm DM,LF,rms} = V_{\rm a,rms} = \frac{M_{\rm VDC}}{2\sqrt{2}} \cdot V_{\rm DC},\tag{4}$$

where the modulation index is defined as  $M_{\rm VDC} = {}^{2V_{\rm ph,pk}}/V_{\rm DC}$ .

Due to symmetry, one  $60^{\circ}$ -sector of a mains period (specifically, the sector where  $v_{\rm a}>v_{\rm b}>v_{\rm c}$ ) is selected to quantify the rms value of the generated CM voltage  $v_{\rm CM}$ . One switching period consists of two active switching states, i.e., [100] and

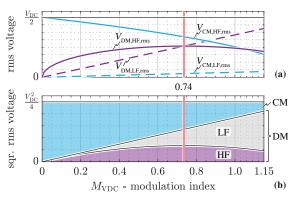

Fig. 4: (a) Analytical rms CM and DM voltages (both LF and HF components) of a two-level 3-Φ voltage DC-link PFC rectifier operating with varying modulation indices  $M_{\rm VDC}$  while maintaining a constant DC-link voltage of  $V_{\rm DC}$  to interface with different 3-Φ mains voltages. (b) Breakdowns of the total squared rms voltage generated by the switching stage, i.e., noise partition variation between CM and DM components, with changing  $M_{\rm VDC}$ . Note that the peak HF DM rms voltage at  $M_{\rm VDC} = 4/(\sqrt{3}\pi) = 0.74$  (solid red line). Also note that  $V_{\rm CM,LE,rms}^2$  is too small to get noticed in (b).

[110], and two zero switching states, i.e., [000] and [111].<sup>3</sup> Note that active states and zero states result in different CM voltage levels, i.e.,  $\pm V_{\rm DC}/6$  for active states and  $\pm V_{\rm DC}/2$  for zero states. Thus, the rms CM voltage of one switching period  $v_{\rm CM,rms}(\varphi)$  at the mains angle  $\varphi$  is

$$v_{\rm CM,rms}(\varphi) = \sqrt{\left(\delta_{100} + \delta_{110}\right) \cdot \frac{V_{\rm DC}^2}{6^2} + \left(\delta_{111} + \delta_{000}\right) \cdot \frac{V_{\rm DC}^2}{2^2}},$$

(5)

where  $\delta_{xxx}$  denotes the dwell time of the active or the zero switching states and varies with the mains angle  $\varphi$ . Finally, the rms CM voltage over one  $60^{\circ}$ -sector (equals the rms CM voltage over the entire mains period)  $V_{\text{CM,rms}}$  is calculated as

$$V_{\text{CM,rms}} = \sqrt{\frac{6}{2\pi} \int_0^{\frac{2\pi}{6}} v_{\text{CM,rms}}^2(\varphi) d\varphi},$$

$$= \sqrt{\frac{1}{4} - \frac{\sqrt{3}M_{\text{VDC}}}{3\pi} \cdot V_{\text{DC}}},$$

(6)

with a detailed derivation in **Appendix A**.

Then, subtracting the CM and LF DM components from  $v_{\text{a'o}}$  leads to the HF DM noise voltage  $v_{\text{DM,HF}}$  (see **Fig. 2c**) according to (1), and thus the HF DM rms noise voltage is

$$V_{\rm DM,HF,rms} = \sqrt{V_{\rm a'o,rms}^2 - v_{\rm DM,LF,rms}^2 - V_{\rm CM,rms}^2},$$

$$= \sqrt{\frac{\sqrt{3}M_{\rm VDC}}{3\pi} - \frac{M_{\rm VDC}^2}{8}} \cdot V_{\rm DC}.$$

(7)

Similarly, the HF CM noise voltage  $v_{\rm CM,HF,rms}$  (see Fig. 2f) is obtained by subtracting the LF CM noise  $v_{\rm CM,LF}$  from the total CM noise voltage  $v_{\rm CM}$ . The rms value of the LF CM

$^3$ The switching state of the two-level 3- $\Phi$  voltage DC-link PFC rectifier is expressed by the states of three bridge legs, e.g., [100], indicating that the high-side switch  $T_{a,h}$  for phase-a and the low-side switches  $T_{b,l}$  and  $T_{c,l}$  for phase-b and phase-c are ON.

noise voltage can be calculated as

$$V_{\text{CM,LF,rms}} = \sqrt{\frac{6}{2\pi} \int_0^{\frac{2\pi}{6}} v_{\text{CM,LF}}^2(\varphi) \, d\varphi},$$

$$= \sqrt{\frac{1}{32} - \frac{3\sqrt{3}}{56\pi} \cdot M_{\text{VDC}} \cdot V_{\text{DC}}},$$

(8)

(see **Appendix A** for a detailed derivation) where the standard SVPWM injects

$$v_{\text{CM,LF}}(\varphi) = \frac{1}{2} \cdot v_{\text{b}}(\varphi),$$

(9)

in the selected  $60^\circ$ -sector ( $v_{\rm a}>v_{\rm b}>v_{\rm c}$ ). Then, the rms value of the HF CM noise voltage is

$$V_{\text{CM,HF,rms}} = \sqrt{V_{\text{CM,rms}}^2 - V_{\text{CM,LF,rms}}^2},$$

$$= \sqrt{\frac{1}{4} - \frac{\sqrt{3}M_{\text{VDC}}}{3\pi} - \left(\frac{1}{32} - \frac{3\sqrt{3}}{56\pi}\right)M_{\text{VDC}}^2 \cdot V_{\text{DC}}}.$$

(10)

Fig. 4a depicts the calculated rms CM and DM voltages (both LF and HF components) of a two-level  $3-\Phi$  voltage DC-link PFC rectifier operating with varying modulation indices  $M_{\rm VDC}$  while maintaining a constant DC-link voltage of  $V_{\rm DC}$  to interface with different  $3-\Phi$  mains voltages. The total squared rms voltage generated by the switching stage consistently equals  $V_{\rm DC}^2/4$ , irrespective of the modulation index  $M_{\rm VDC}$ . The variation in the noise partition between CM and DM components, which changes with different  $M_{\rm VDC}$ , is of great interest, and is further explained by considering the total squared rms voltage and its breakdown in Fig. 4b.

With an increase in  $M_{\rm VDC}$ , the dwell times of zero switching states decrease linearly, and the dwell times of active switching states increase linearly. It's noteworthy that the CM voltages generated by the zero switching states consistently surpass those of the active switching states, i.e.,  $\pm V_{\rm DC}/6$  for active states and  $\pm V_{\rm DC}/2$  for zero states. Consequently, (6) indicates a linear reduction in the total (including HF and LF) squared rms CM voltages  $V_{\rm CM,rms}^2$  and, thus, a linear increase in the total squared rms DM voltages  $V_{\rm DM,rms}^2$ . The LF CM voltage  $V_{\rm CM,LF,rms}$ , i.e., proportional to  $M_{\rm VDC}$  [see (8)], results in a monotonic decrease in the CM pre-filter noise  $V_{\rm CM,HF,rms}$  with an increasing  $M_{\rm VDC}$ .

The total squared DM voltage  $V_{\rm DM,rms}^2$  shows a linear increase with  $M_{\rm VDC}$ , and  $V_{\rm DM,LF,rms}^2$  experiences a quadratic growth [see (4)]. This leads to  $V_{\rm DM,HF,rms}^2$  taking the form of a downward-opening parabola, peaking at  $M_{\rm VDC}=4/(\sqrt{3}\pi)=0.74$ . Importantly, this outcome remains independent of  $V_{\rm DC}$  and can be computed using (7).

Finally, the analytical envelopes for the DM and CM prefilter voltage spectra at frequencies  $f \ge f_{\rm sw}$  are expressed as

$$V_{\rm DM,VDC}(f) = V_{\rm DM,HF,rms}(V_{\rm DC}, M_{\rm VDC}) \cdot f_{\rm sw}/f, \qquad (11)$$

$$V_{\text{CM,VDC}}(f) = V_{\text{CM,HErms}}(V_{\text{DC}}, M_{\text{VDC}}) \cdot f_{\text{sw}}/f,$$

(12)

where the expressions for the HF rms values obtained in (7) and (10) are used, respectively.

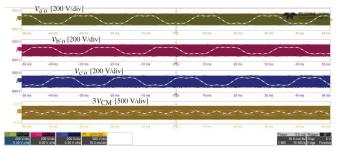

Fig. 5: Measured switch-node voltages  $v_{a'o}$ ,  $v_{b'o}$ , and  $v_{c'o}$ , and CM voltage  $v_{\rm CM}$  when operating the 3- $\Phi$  two-level voltage DC-link hardware demonstrator from [25] at a 400 V mains with standard SVPWM, an output voltage of 800 V, an output power of 10 kW, and a switching frequency of 100 kHz; the LF voltage components are indicated (see also Fig. 2a and Fig. 2e). The key specifications of this hardware demonstrator are listed in Tab. I.

# B. Experimental Verification

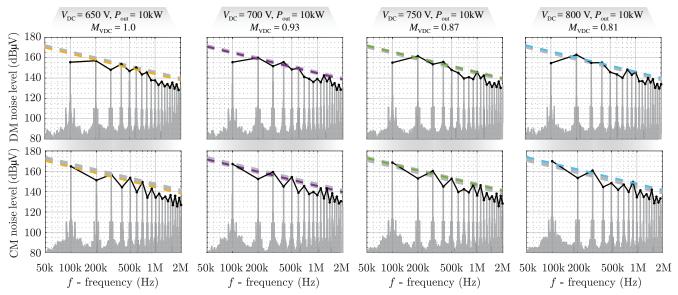

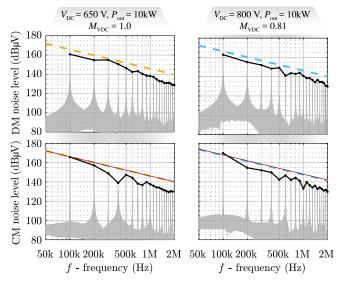

The spectra of the DM and CM pre-filter noise voltages,  $v_{\rm DM,HF}$  and  $v_{\rm CM,HF}$ , are then experimentally quantified by post-processing the measured  $v_{\rm a'o}$ ,  $v_{\rm b'o}$ , and  $v_{\rm c'o}$  of a two-level voltage DC-link hardware demonstrator (see Fig. 5) using (1) and (2), and for several operating points with different DC-link voltages and hence different modulation indices. The key specifications of this hardware demonstrator are listed in Tab. I. Fig. 6 shows the amplitude spectra of the measured  $v_{\rm DM,HF}$  and  $v_{\rm CM,HF}$  and compares them against the analytical envelopes from (11) and (12), respectively. Excellent agreement between the calculated envelopes and the measured amplitude spectra can be observed for the common modulation index range of  $M_{\rm VDC}=0.8$  to  $M_{\rm VDC}=1.0$ .

Generic characteristics of the voltage DC-link rectifier's DM and CM pre-filter noise emissions can be summarized based on the derived analytical envelopes:

- The DM envelopes  $V_{\rm DM,VDC}(f)$  indicate that the DM noise emission level depends solely on the switched voltage, i.e., the DC-link voltage  $V_{\rm DC}$  (or, equivalently, the 3- $\Phi$  input voltage  $V_{\rm ph,pk}$ ) and the modulation index  $M_{\rm VDC}$  but not the output power. Since PFC rectifiers typically operate with high modulation indices within a relatively narrow range, the impact of  $M_{\rm VDC}$  is limited, which can be clearly observed in **Fig. 6**.

- The CM envelopes  $V_{\rm CM,VDC}(f)$  reveal that the CM noise emission level is again determined by the DC-link voltage  $V_{\rm DC}$  (or, equivalently, the 3- $\Phi$  input voltage  $V_{\rm ph,pk}$ ) and the modulation index  $M_{\rm VDC}$ .

- As both DM and CM mode pre-filter noise emissions are DC-link voltage-dependent but largely independent of the power level, the total EMI noise emission, i.e., the voltage ultimately measured across the LISN resistance R<sub>m</sub>, is also largely independent of the output power.

# III. EMI Pre-Filter Noise Emission of Three-Phase Current DC-Link PFC Rectifier Systems

$3-\Phi$  buck-type current DC-link PFC rectifiers (see **Fig. 7a**) offer the advantage of requiring a reduced number of main magnetic components, specifically just one DC-link inductor, as opposed to three inductors on the AC side for voltage DC-link converters (see **Fig. 1a**). This allows for more compact

Fig. 6: DM (top row) and CM (bottom row) pre-filter noise amplitude spectra (the black solid lines indicate the envelopes of the measured spectra) extracted from measurements (see Fig. 5) of a  $10 \,\mathrm{kW}$  two-level  $3\text{-}\Phi$  voltage DC-link PFC rectifier interfacing a  $400 \,\mathrm{V}$  mains using different DC-link voltages  $V_{DC}$  (different modulation indices  $M_{VDC}$ ) and a switching frequency of  $f_{sw} = 100 \,\mathrm{kHz}$ . The dashed envelopes are obtained with the low-complexity analytical expressions (11) for DM and (12) for CM, and are grouped by colors according to the respective operating points; the envelopes corresponding to the respective other three operating points are shown in gray for reference.

**TABLE I:** System specifications the  $3-\Phi$  two-level voltage DC-link hardware demonstrator from [25].

|                        | Description           | Value                                   |  |  |

|------------------------|-----------------------|-----------------------------------------|--|--|

| $\overline{V_{ m in}}$ | Rms input mains volt. | 400 V                                   |  |  |

| $V_{\rm DC}$           | DC output volt. range | $650\mathrm{V}$ $800\mathrm{V}$         |  |  |

| $I_{\mathrm{DC}}$      | DC output current     | $15.4\mathrm{A}\ \dots\ 12.5\mathrm{A}$ |  |  |

| $M_{ m VDC}$           | Modulation index      | 1.0 0.81                                |  |  |

| $P_{\text{out}}$       | Output power          | $10\mathrm{kW}$                         |  |  |

| $f_{ m sw}$            | Switching frequency   | 100 kHz                                 |  |  |

hardware realization and less labor-intensive manufacturing [16]. Additionally, the 3- $\Phi$  current DC-link converter inherently generates continuous sinusoidal 3- $\Phi$  voltages, making it an attractive solution for motor inverters [20]–[22], [26].

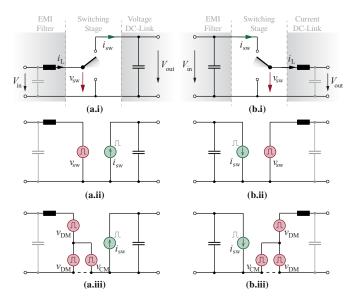

In contrast to voltage DC-link converters, current DC-link converters typically feature a constant DC-link *current*. The switching stage consists of an upper and a lower commutation cell, each consisting of three switches with bipolar voltage-blocking capability, and AC-side commutation capacitors. Each commutation cell can route the constant DC-link current to one of the three phase terminals, resulting in the six active and three zero/freewheeling switching states shown in **Fig. 7b**. Note that these switching states correspond to *current* SVs: the desired  $3-\Phi$  sinusoidal input currents are generated by using current DC-link SVPWM to synthesize the desired input current SV  $\vec{i}^*$ , i.e., the DC-link current is essentially distributed to the three phases using PWM, which is further explained in **Appendix B**.

The DM and CM equivalent circuits of the switching stage are then shown in **Fig. 7c**. Taking phase a as an example, the DM behavior of the current DC-link rectifier can be modeled by the switched current pulses  $i'_a$ , which can further be decomposed into the contributions from the upper  $i'_{ap}$  and

the lower  $i_{\rm an}^{'}$  commutation cells. Then, the pre-filter DM EMI noise can be quantified by the voltage that appears across the LISN measurement resistor  $R_{\rm m}$  as a consequence of the HF components of  $i_{\rm a}^{'}$  flowing through it (note that the LISN's decoupling capacitor prevents the LF components of  $i_{\rm a}^{'}$  from flowing through  $R_{\rm m}$ ), i.e.,

$$v_{\rm DM,HF} = i'_{\rm a,HF} \cdot R_{\rm m} = (i'_{\rm ap,HF} + i'_{\rm an,HF}) \cdot R_{\rm m}.$$

(13)

The CM voltage of the 3- $\Phi$  current DC-link PFC rectifier can be obtained from the two switch-node voltages ( $v_{\rm nk}$  and  $v_{\rm pk}$ ) as shown in **Fig. 7c**

$$v_{\text{CM}} = \frac{1}{2} \cdot (v_{\text{no}} + v_{\text{po}}) = \frac{1}{2} \cdot (v_{\text{nk}} + v_{\text{pk}}),$$

(14)

considering that the 3- $\Phi$  filter capacitor voltages are nearly equal to the 3- $\Phi$  mains voltages and the artificial neutral point (start point of filter capacitor) k can be assumed at the potential o. Note again that the worst case for the CM noise measurement is assumed by connecting the negative output terminal to PE, and, neglecting the impedance of the DC output capacitor at HF, implicitly also the positive terminal. Furthermore, considering the DM DC-link inductance  $L_{DC}$  is provided by two windings arranged on a single magnetic core with nearly ideal inverse coupling, only the leakage inductance  $L_{\sigma}$  contributes to the DC-link CM impedance, which is very low and, thus, can be neglected such that the CM noise source is directly connected to the LISN. Similar to modeling the voltage DC-link converter, this worst case for CM noise emissions is ensured by shorting the parasitic capacitances, which would be in series with the LISN measurement resistors as voltage dividers, and by disconnecting the capacitances, which would be connected in parallel to the LISN measurement resistors as current shunts. Both effects would result in reduced CM noise emissions. Fig. 8 shows simulated key waveforms of the LF

Fig. 7: (a) Power circuit of a 3- $\Phi$  buck-type current DC-link PFC rectifier (including an EMI filter stage where AC-side filter/commutation capacitors are shown as the first filtering components) connected to the mains via a LISN. (b) The rectifier's switching stage can generate six active and two zero current space vectors (SVs) at the switching nodes; the switching states are defined by the turned-on transistors of the high-side and low-side commutation cells as, for example, [ac], which indicates that the DC-link current flows through  $T_{c,l}$ , respectively. SVPWM is typically used to synthesize a desired local average input current SV  $\vec{i}^*$ . (c) DM and CM equivalent circuits where the switching stage is modeled as LF and HF current sources for DM and as LF and HF voltage sources for CM; the HF DM current sources and CM voltage sources represent the respective pre-filter noise emissions.

#### and HF DM currents and CM voltages.

## A. Analytical DM and CM Pre-Filter Noise Envelopes

The same approach as used in [24] and introduced above in **Section II-A** is now applied to the current DC-link converter. Using phase a as an example, the switching stage input current  $i_a'$  (see **Fig. 8a**) is a switched current waveform attaining the values  $+I_{\rm DC}$ , 0 (during the zero switching state [aa] for phase a), and  $-I_{\rm DC}$ , i.e., three current values and not only two voltage values as was the case for the voltage DC-link system above. Thus, the total DM rms current value has to be calculated considering quarter-wave symmetry within one mains period as

$$I_{\text{DM,rms}} = i_{\text{a,rms}}^{'} = \sqrt{\frac{2}{\pi} \int_{0}^{\frac{\pi}{2}} [d_{\text{a}}(\varphi) \cdot I_{\text{DC}}^{2}] d\varphi},$$

$$= \sqrt{\frac{2M_{\text{CDC}}}{\pi}} \cdot I_{\text{DC}},$$

(15)

where  $M_{\rm CDC} = I_{\rm ph,pk}/I_{\rm DC}$  is the modulation index and  $d_{\rm a} = |i_{\rm a}|/I_{\rm DC}$  is the duty cycle of phase a, which is independent of the modulation scheme (i.e., the switching state sequence and the selection of the zero states, see below), and a detailed

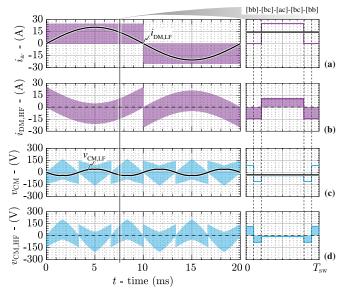

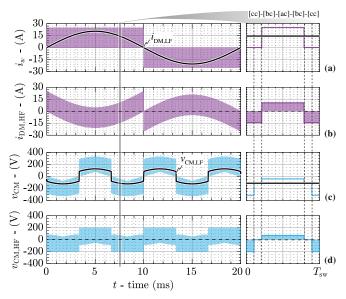

**Fig. 8:** Simulated key waveforms (with a zoomed view over one switching period) of the 3- $\Phi$  current DC-link PFC rectifier (see **Fig. 7a**) operating with reduced CM SVPWM from a 400 V (line-to-line rms) mains with 400 V DC output voltage, 10 kW output power, and a DC-link current of 25 A. Taking phase a as an example, (**a**) shows the total DM input current  $i_a$  and (**b**) its HF component  $i_{\rm DM,HF}$ ; (**c**) shows the total CM noise voltage  $v_{\rm CM}$  and (**d**) its HF component  $v_{\rm CM,HF}$ , i.e., (**b**) and (**d**) indicate the pre-filter DM and CM noise emissions.

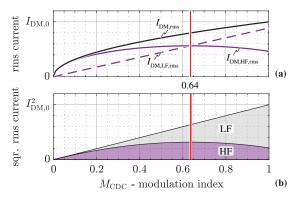

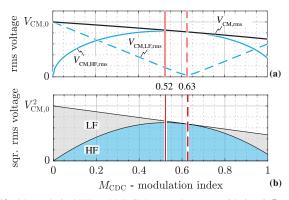

Fig. 9: (a) Analytical HF and LF DM rms currents of a 3- $\Phi$  current DC-link PFC rectifier interfacing a 400 V mains with varying modulation indices  $M_{\rm CDC}$  while maintaining a constant DC-link current of  $I_{\rm DC}$  to supply different DC output voltages. (b) Breakdowns of the total squared rms DM currents generated by the switching stage, i.e., the LF and HF components with different modulation indices  $M_{\rm CDC}$ . Note that a maximum HF DM rms current is observed when  $M_{\rm CDC}=2/\pi=0.64$  (solid red line).

derivation is provided in **Appendix B**. Then, excluding the fundamental component, i.e., the desired phase current  $i_a$  from  $i_{DM}$  results in the HF DM rms current (see **Fig. 8b**)

$$I_{\rm DM,HF,rms} = \sqrt{I_{\rm DM,rms}^2 - i_{\rm a,rms}^2},$$

=  $\sqrt{\frac{2M_{\rm CDC}}{\pi} - \frac{M_{\rm CDC}^2}{2}} \cdot I_{\rm DC}.$  (16)

**Fig. 9** illustrates the analytical, i.e., using (15) and (16), LF and HF rms DM currents of a 3- $\Phi$  current DC-link PFC rectifier interfacing a 400 V mains with varying modulation indices  $M_{\rm CDC}$  while maintaining a constant DC-link current  $I_{\rm DC}$  to supply different DC output voltages. An increase in

$M_{\rm CDC}$  leads to reduced dwell times of zero switching states and, consequently, an increase in the total DM noise  $I_{\rm DM,rms}^2$  generated by the switching stage. This was not the case in the aforementioned voltage DC-link converter, where the total noise source generated by the switching stage consistently equals  $V_{\rm DC}^2/4$  (see **Fig. 4b**).  $I_{\rm DM,rms}^2$  is linearly proportional to  $M_{\rm CDC}$ , reaching its maximum value of  $I_{\rm DM,0}=\sqrt{2/\pi}I_{\rm DC}$  at  $M_{\rm CDC}=1$  [see (15)]. However, its LF component  $I_{\rm DM,LF,rms}^2$  is quadratically proportional to  $M_{\rm CDC}$  [see (16)]. This results in  $I_{\rm DM,HF,rms}^2$  obtaining the shape of a downward-opening parabola, attaining its maximum at  $M_{\rm CDC}=2/\pi=0.64$ .

The CM noise emission of the calculated  $3-\Phi$  current DC-link rectifier depends on the applied switching states, i.e., on the specific SVPWM method employed. A  $30^{\circ}$ -sector of one mains period ( $v_{\rm a}>v_{\rm b}>0>v_{\rm c}$ , see **Fig. 7b**) is selected where the switching states [bb], [bc], and [ac] are used according to the implemented SVPWM with reduced CM [16], [27]. The rms CM voltage of one switching period  $v_{\rm CM,rms}(\varphi)$  at a mains angle  $\varphi$  is first calculated as

$$v_{\rm CM,rms}(\varphi) = \sqrt{\delta_{\rm ac} \cdot v_{\rm CM,ac}^2 + \delta_{\rm bc} \cdot v_{\rm CM,bc}^2 + \delta_{\rm bb} \cdot v_{\rm CM,bb}^2}, (17)$$

where, e.g.,  $\delta_{\rm ac}$  is the dwell time of the switching state [ac] with the CM voltage of  $v_{\rm CM,ac} = (v_a + v_c)/2$ ;  $v_a$  and  $v_c$  denote the phase voltages of the phases a and c, respectively.<sup>4</sup> Then, the total CM noise emission  $V_{\rm CM,rms}$  (see **Fig. 8c**) can be obtained by integrating the local average value (rms CM voltage of one switching period) over the selected  $30^{\circ}$ -sector:

$$V_{\text{CM,rms}} = \sqrt{\frac{6}{\pi} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} v_{\text{CM,rms}}^2(\varphi) \, d\varphi},$$

$$= \sqrt{\frac{8\sqrt{3} - 15}{8\pi} M_{\text{CDC}} + \frac{2\pi - 3\sqrt{3}}{4\pi} \cdot V_{\text{ph,pk}}},$$

(18)

with a detailed derivation provided in **Appendix B**.

Furthermore, the rms value of the LF CM voltage is calculated by first defining the local average (not rms) CM voltage  $v_{\rm CM,LF}(\varphi)$  as

$$v_{\text{CM,LF}}(\varphi) = \delta_{\text{ac}} \cdot v_{\text{CM,ac}} + \delta_{\text{bc}} \cdot v_{\text{CM,bc}} + \delta_{\text{bb}} \cdot v_{\text{CM,bb}}, \quad (19)$$

with a detailed derivation provided in **Appendix B**. Then, the rms value of LF CM voltage over the selected 30°-sector (same as over one mains period) becomes

$$V_{\text{CM,LF,rms}} = \sqrt{\frac{6}{\pi}} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} v_{\text{CM,LF}}^{2}(\varphi) d\varphi,$$

$$= \sqrt{\frac{2\pi - 3\sqrt{3}}{4\pi} - \frac{\sqrt{3}}{2\pi} M_{\text{CDC}} + \frac{12\pi - 9\sqrt{3}}{32\pi} M_{\text{CDC}}^{2}} \cdot V_{\text{ph,pk}}.$$

(20)

Subtracting the LF CM voltage  $v_{\rm CM,LF}$ , from the total CM

**TABLE II:** System specifications the  $3-\Phi$  buck-type current DC-link PFC rectifier hardware demonstrator from [16].

|                     | Description           | Value                             |  |  |

|---------------------|-----------------------|-----------------------------------|--|--|

| $\overline{V_{in}}$ | Rms input mains volt. | 400 V                             |  |  |

| $V_{\rm DC}$        | DC output volt. range | $300\mathrm{V}\dots450\mathrm{V}$ |  |  |

| $I_{\mathrm{DC}}$   | DC output current     | 25 A                              |  |  |

| $M_{\rm CDC}$       | Modulation index      | $0.61 \dots 0.92$                 |  |  |

| $P_{\text{out}}$    | Output power          | $7.5\mathrm{kW}$ $10\mathrm{kW}$  |  |  |

| $f_{ m sw}$         | Switching frequency   | $100\mathrm{kHz}$                 |  |  |

voltage  $v_{\rm CM}$  results in the HF CM noise rms voltage

$$V_{\text{CM,HF,rms}} = \sqrt{V_{\text{CM,rms}}^2 - V_{\text{CM,LF,rms}}^2},$$

$$= \sqrt{\frac{12\sqrt{3} - 15}{8\pi} M_{\text{CDC}} + \frac{9\sqrt{3} - 12\pi}{32\pi} M_{\text{CDC}}^2} \cdot V_{\text{ph,pk}}.$$

(21)

Fig. 10 illustrates the analytical LF and HF rms CM voltages of a 3- $\Phi$  current DC-link PFC rectifier interfacing a  $400\,\mathrm{V}$  mains with varying modulation indices  $M_{\mathrm{CDC}}$  while maintaining a constant DC-link current to supply different DC output voltages. The total CM noise  $V_{\mathrm{CM,rms}}^2$  generated by the switching stage varies with the modulation indices  $M_{\mathrm{CDC}}$  since shortened dwell times of zero switching states are needed as  $M_{\mathrm{CDC}}$  increases; and, for the PFC operation, zero switching states contributes to larger CM noise (see Fig. 8c).

Furthermore, in PFC operation, active and zero switching states generate CM voltages with opposite signs (see Appendix B). This results in a curve of  $V_{\rm CM,LF,rms}$  exhibiting a turning point, i.e.,  $M_{\rm CDC} = {}^{8\sqrt{3}}/({}^{12\pi-9\sqrt{3}}) = 0.63$  (dashed vertical line), where it transitions from a descending to an ascending slope (see Fig. 10). In the range of  $M_{\rm CDC} < 0.63$ , CM voltages of zero switching states dominate, such that an increased  $M_{\rm CDC}$  results in shorter dwell times of zero switching state and reduced  $V_{\rm CM,LF,rms}$ . When  $M_{\rm CDC} > 0.63$ , active switching states become dominant, causing an increase in  $V_{\rm CM,LF,rms}$  with  $M_{\rm CDC}$ . Consequently, the HF pre-filter CM voltage  $V_{\rm CM,HF,rms}$  obtains a convex shape with a maximum value at  $M_{\rm CDC} = ({}^{8\sqrt{3}-10})/({}^{4\pi-3\sqrt{3}}) = 0.52$  (solid red line) as shown in Fig. 10.

Finally, the analytical envelopes of the pre-filter DM and CM voltage spectra for frequencies  $f \ge f_{\rm sw}$  are

$$V_{\rm DM,CDC}(f) = I_{\rm DM,HF,rms}(I_{\rm DC}, M_{\rm CDC}) \cdot R_{\rm m} \cdot f_{\rm sw}/f, \qquad (22)$$

$$V_{\text{CM,CDC}}(f) = V_{\text{CM,HF,rms}}(V_{\text{ph,pk}}, M_{\text{CDC}}) \cdot f_{\text{sw}}/f, \tag{23}$$

where the expressions for the HF rms values obtained in (16) and (21) are used, respectively; note further the multiplication with the LISN measurement resistor  $R_{\rm m}$  in (22) as explained above in the context of (13).

# B. Experimental Verification

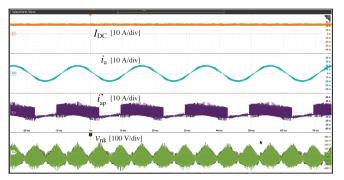

The spectra of the DM and CM EMI noise voltages  $i_{\rm DM}$  and  $v_{\rm CM}$  are then experimentally quantified as shown in Fig. 11 using the hardware demonstrator of [16]. The key specifications of this hardware demonstrator are listed in Tab. II. Since the three AC-side filter capacitors are realized by several parallel film capacitors interconnected by copper

<sup>&</sup>lt;sup>4</sup>In the switching state [ac], the lower switch node n is connected to phase c and the upper switch node p is connected to phase a; hence,  $v_{\rm nk}=v_{\rm c}$  and  $v_{\rm pk}=v_{\rm a}$  in (14).

**Fig. 10:** (a) Analytical HF and LF CM rms voltages considering 3-Φ current DC-link PFC rectifier interfacing a 400 V mains with different modulation indices  $M_{\rm CDC}$  and a constant DC-link current of  $I_{\rm DC}$  to supply different DC output voltages. (b) illustrates the squared rms CM voltage and its breakdown into LF and HF components with different modulation indices  $M_{\rm CDC}$ . Note that a maximum HF CM rms voltage is observed when  $M_{\rm CDC} = (8\sqrt{3}-10)/(4\pi-3\sqrt{3}) = 0.52$  (solid red line) and a minimum LF CM rms voltage is attained when  $M_{\rm CDC} = 8\sqrt{3}/(12\pi-9\sqrt{3}) = 0.63$  (dashed red line).

Fig. 11: Measurement results when operating the demonstrator from [16] at a 400 V mains with reduced CM SVPWM [27], an output voltage of 400 V, an output power of  $10\,\mathrm{kW}$ , and a switching frequency of  $100\,\mathrm{kHz}$ . In addition to the DC-link current,  $I_\mathrm{DC}$ , the (filtered) input current of phase a,  $i_\mathrm{a}$ , the switched transistor current  $i'_\mathrm{ap}$  (see also Fig. 7a) and the voltage  $v_\mathrm{nk}$  are shown. Similarly, the currents  $i'_\mathrm{an}$  and the voltage  $v_\mathrm{pk}$  are measured (not shown), which allows to calculate  $v_\mathrm{DM,HF}$  from (13) and  $v_\mathrm{cm}$  from (14). Note a small phase shift between  $i_\mathrm{a}$  and  $i'_\mathrm{ap}$  due to the capacitive current flowing through the first-stage filter capacitors. The key specifications of this hardware demonstrator are listed in Tab. II.

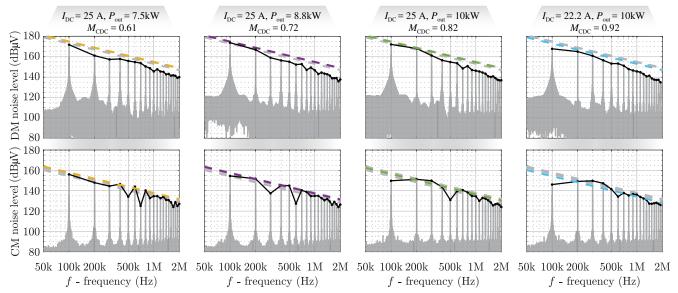

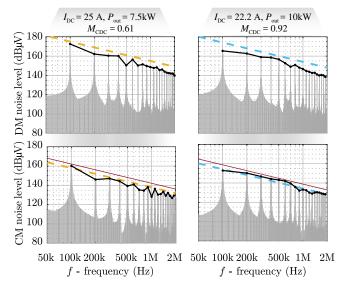

planes in a printed circuit board, it is not possible to directly measure  $i_{\rm a}'$ , i.e., the total phase-a input current of the switching stage. Instead, its two components (see **Fig. 7a**) contributed by the top  $(i_{\rm ap}')$  and the bottom  $(i_{\rm an}')$  commutation cells are individually measured by placing Rogowski coils (PEM CWT1BUM) around the drain legs of the transistor's TO-247 packages. These measured currents are then superimposed to obtain  $i_{\rm a}'$ , and the DM pre-filter noise voltage  $v_{\rm DM,HF}$  follows from (13). The CM pre-filter noise voltage  $v_{\rm CM,HF}$  is obtained according to (14) by measuring  $v_{\rm nk}$  and  $v_{\rm pk}$ . **Fig. 12** shows the amplitude spectra of the experimentally obtained  $v_{\rm DM,HF}$  and  $v_{\rm CM,HF}$ , and compares them against the analytical envelopes from (22) and (23), respectively. Again, excellent agreement between the analytical envelopes and the measured spectra can be observed.

Generic characteristics of the current DC-link rectifier regarding its DM and CM pre-filter noise emissions can be summarized based on the derived analytical envelopes:

- The DM envelopes  $V_{\rm DM,CDC}$  clearly show that the DM noise emission level is proportional to the DC-link current  $I_{\rm DC}$  and depends on the modulation index  $M_{\rm CDC}$ , i.e., it is power-dependent for a given mains voltage level.

- The CM envelopes  $V_{\rm CM,CDC}$  reveal that the CM noise emission level is proportional to the 3- $\Phi$  mains voltage  $V_{\rm ph,pk}$  and also depends on the modulation index  $M_{\rm CDC}$ .

- Note that the CM noise levels are far (in the order of 20 dB) below the DM noise levels (see Fig. 12). Thus, the total EMI noise emission, i.e., the voltage ultimately measured across the LISN resistance R<sub>m</sub>, is dominated by the DM components, which are mostly dependent on the DC-link current and/or output power [16] but not on the mains voltage; note that the voltage DC-link rectifier shows opposite characteristics (see Section II-B).

#### IV. EMI Noise Emissions Comparison

As the derived analytical approximations for DM and CM pre-filter noise emissions of both voltage DC-link and current DC-link PFC rectifiers show a close match with measurements, they enable a straightforward and generic comparison of voltage DC-link and current DC-link converters regarding the pre-filter EMI noise emissions and, consequently regarding the required EMI filter attenuation.

The DM pre-filter n oise level of the v oltage DC-link PFC rectifier  $V_{\rm DM,VDC}(f)$  d epends on the D C-link v oltage  $V_{\rm DC}$  while the DM noise source level of the current DC-link PFC rectifier  $V_{\rm DM,CDC}(f)$  is proportional to the DC-link current  $I_{\rm DC}$ . Considering typical modulation indices of  $M_{\rm VDC}=1$  for the voltage DC-link PFC rectifier and of  $M_{\rm CDC}=0.85$  for the current DC-link PFC rectifier, the HF DM rms voltage  $V_{\rm DM,HF,rms}$  of voltage DC-link PFC rectifier according to (7) is

$$V_{\rm DM,HF,rms} = \sqrt{\frac{4\sqrt{3}}{3\pi M_{\rm VDC}}} - \frac{1}{2} \cdot V_{\rm ph,pk} \approx 0.5 V_{\rm ph,pk},$$

(24)

and the HF DM rms current  $I_{DM,HF,rms}$  of current DC-link PFC rectifier according to (16) is

$$I_{\text{DM,HF,rms}} = \sqrt{\frac{2}{\pi M_{\text{CDC}}}} \quad \frac{1}{2} \cdot I_{\text{ph,pk}} \approx 0.5 I_{\text{ph,pk}}.$$

(25)

Then, both rectifiers  $\overline{g}$  enerate equal DM pre-filter noise emissions if the equivalent 3- $\Phi$  AC resistance the converter represents to the mains, i.e.,  $R_{AC} = V_{ph,pk}/I_{ph,pk}$ , approximately equals the LISN measurement resistance  $R_{m}$ :

$$V_{\rm DM,HF,rms} = I_{\rm DM,HF,rms} \cdot R_{\rm m}$$

$$\Rightarrow V_{\rm DM,HF,rms} / I_{\rm DM,HF,rms} = R_{\rm m},$$

(26)

and considering (24) and (25), we have

$$V_{\rm DM,HF,rms}/I_{\rm DM,HF,rms} = V_{\rm ph,pk}/I_{\rm ph,pk} = R_{\rm AC} \Rightarrow R_{\rm AC} \approx R_{\rm m}.$$

(27)

For higher equivalent AC resistances  $R_{\rm AC} > R_{\rm m}$ , i.e., lower mains current fundamentals at given mains voltage, the DM

$^5$ Note that the maximum modulation index without over-modulation equals  $M_{\rm VDC,max}=2/\sqrt{3}=1.15$  for voltage DC-link and  $M_{\rm CDC,max}=1$  for current DC-link converter, i.e., a modulation reserve of about 15% is considered for both converters.

Fig. 12: DM (top row) and CM (bottom row) pre-filter noise amplitude spectra (the black solid lines indicate the envelopes of the measured spectra) extracted from measurements (see Fig. 11) of a  $10\,\mathrm{kW}$  3- $\Phi$  current DC-link PFC rectifier interfacing a  $400\,\mathrm{V}$  mains using reduced CM SVPWM at a switching frequency of  $100\,\mathrm{kHz}$  to supply four different output power levels with the maximum DC-link current of  $25\,\mathrm{A}$  (hardware limitation in [16]), i.e., different modulation indices  $M_{\mathrm{CDC}}$  are applied. The dashed envelopes are obtained with the low-complexity analytical expressions (22) for DM and (23) for CM, and are grouped by colors according to the respective operating points; the envelopes corresponding to the respective other three operating points are shown in gray for reference.

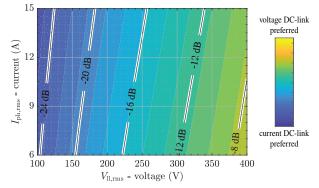

Fig. 13: Ratio of DM pre-filter noise levels of current D C-link and voltage DC-link converters in decibels, i.e.,  $20\log_{10}\left(V_{\rm DM,CDC}(f)/V_{\rm DM,VDC}(f)\right)$ , in dependence of the mains line-to-line rms voltage  $V_{\rm ll,rms}$  and the output power  $P_{\rm out}$  considering typical nominal modulation indices of  $M_{\rm VDC}=1$  for voltage DC-link converters and of  $M_{\rm CDC}=0.85$  for current DC-link converters.

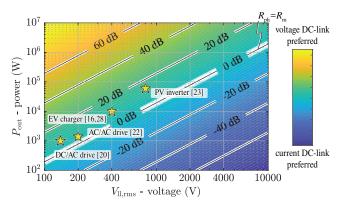

pre-filter noise emission of a current DC-link PFC rectifier is lower than that of a voltage DC-link PFC rectifier; whereas for lower AC equivalent resistance  $R_{\rm AC} < R_{\rm m}$ , i.e., higher mains current fundamentals at given mains voltage, the voltage DC-link PFC rectifier achieves lower DM pre-filter noise levels. Thus, **Fig. 13** shows the ratio  $V_{\rm DM,CDC}/V_{\rm DM,VDC}$  in dependence of the mains line-to-line rms voltage  $V_{\rm Il,rms}$  and the output power  $P_{\rm out}$ , considering  $R_{\rm m}=50\,\Omega$ . Generally, considering the required DM EMI filter attenuation (and hence size/effort), the voltage DC-link PFC rectifier is preferred for high-power applications at relatively low mains voltages; conversely, the current DC-link solution becomes more attractive for applications with higher mains voltages and/or lower power levels. **Fig. 13** also highlights a few current DC-link and voltage DC-link systems discussed in the recent literature for various appli-

**Fig. 14:** Ratio of CM pre-filter noise levels of current DC-link and voltage DC-link motor drive inverters in decibels, i.e.,  $20\log_{10}\left(V_{\text{CM,CDC}}(f)/V_{\text{CM,VDC}}(f)\right)$  in dependence of line-to-line rms motor voltage  $V_{\text{II,rms}}$  and phase rms motor current  $I_{\text{ph,rms}}$ . The exemplary  $10\,\mathrm{kW}$  motor drive system features a nominal motor voltage of  $400\,\mathrm{V}$  (line-to-line, rms) and nominal modulation indices of  $M_{\text{VDC}}=1$  and  $M_{\text{CDC}}=0.85$ . Note that a nominal constant DC-link voltage of  $650\,\mathrm{V}$  for the voltage DC-link system and a nominal constant DC-link current of  $24\,\mathrm{A}$  for the current DC-link system are maintained during operation with reduced AC current or voltages.

cations, e.g., for EV charger modules [16], [28], PV inverters [23], DC/AC motor inverters [20], and AC/AC motor drives [22]. These applications exhibit system requirements resulting in  $R_{\rm AC} \approx R_{\rm m}$ , i.e., similar DM pre-filter noise levels and hence similar EMI filter realization effort is expected for current DC-link and voltage DC-link solutions. This underscores the importance of comprehensive, multi-dimensional comparisons between the two converter types under such scenarios.

The CM pre-filter voltage noise levels of both, voltage and current DC-link converters depend on the mains voltage and the modulation index. Assuming again typical modulation indices of  $M_{\rm VDC}=1$  for the voltage DC-link rectifier and of

$M_{\rm CDC}=0.85$  for the current DC-link rectifier, the ratio of the CM noise levels when interfacing the same 3- $\Phi$  mains becomes

$$V_{\text{CM,CDC}}(f)/V_{\text{CM,VDC}}(f) = 37.7\% = -8.5 \,\text{dB}.$$

(28)

This implies that the current DC-link topology, in typical cases<sup>6</sup>, generates less CM EMI noise compared to the voltage DC-link topology. This observation is further supported by comparing the absolute values of the CM noise emission in **Fig. 6** and **Fig. 12**.

Current DC-link converters, using the modulation scheme with reduced CM noise emissions (see **Section III**), generate relatively low CM pre-filter noise compared to voltage DC-link converters, which can be explained by their respective switched CM voltage noise sources: The CM voltage levels of a voltage DC-link converter are determined solely by the DC-link voltage level (see **Fig. 2e** for the CM voltage waveforms), i.e.,

$$\pm V_{DC}/2 = \pm 325 \,\mathrm{V}$$

, and  $\pm V_{DC}/6 = \pm 108 \,\mathrm{V}$ ,

considering a typical modulation index  $M_{\rm VDC}=1$  to interface a 400 V (line-to-line rms) mains with a DC-link voltage of 650 V. However, the CM voltage levels of a current DC-link converter are determined by the 3- $\Phi$  AC input voltages (see **Appendix B**). In the selected 30°-sector of one mains period  $(v_a > v_b > 0 > v_c$ , see **Fig. 7b**), the voltage levels

$$\begin{split} 0\,\mathrm{V} &< v_{\mathrm{CM,[bb]}} = v_{\mathrm{b}} < v_{\mathrm{ph,pk}}/2 = 163\,\mathrm{V}, \\ -81\,\mathrm{V} &= -V_{\mathrm{ph,pk}}/4 < v_{\mathrm{CM,[ac]}} = (v_{\mathrm{a}} + v_{\mathrm{c}})/2 < 0\,\mathrm{V}, \\ -140\,\mathrm{V} &= -\sqrt{3}V_{\mathrm{ph,pk}}/4 < v_{\mathrm{CM,[bc]}} = (v_{\mathrm{b}} + v_{\mathrm{c}})/2 < -V_{\mathrm{ph,pk}}/4 = -81\,\mathrm{V}, \end{split}$$

are attained by the CM voltage (see **Fig. 8c** for the CM voltage waveforms). Due to phase symmetry, a full mains period can be reconstructed by mirroring and/or inverting the selected 30°-sector. Therefore, analyzing only the 30°-sector is sufficient to represent the entire mains period without any loss of generality. Finally, in contrast to voltage DC-link converters, relatively low amplitudes of the CM (switched voltage) noise sources lead to low CM noise emissions of current DC-link converters.

CM noise levels are of particular interest in the context of motor drive systems, where CM currents might, for example, damage mechanical bearings [29], [30]. Therefore, **Fig. 14** compares the pre-filter CM noise levels of voltage DC-link and current DC-link systems considering an exemplary  $10 \,\mathrm{kW}$  motor drive system with a nominal motor voltage of  $400 \,\mathrm{V}$  (line-to-line, rms) and again assuming typical nominal modulation indices for the voltage DC-link converter  $M_{\mathrm{VDC}} = 1$  and the current DC-link converter  $M_{\mathrm{CDC}} = 0.85$ . The figure covers the typical torque/speed (current/voltage) range of a permanent magnet synchronous motor operating with a near-unity power factor. It can be observed that the current DC-link topology generates lower CM pre-filter noise compared to the

<sup>6</sup>Current DC-link converters typically operate using a modulation scheme that achieves a reduced CM voltage without sacrificing switching losses, a technique known as RCM SVPWM [27]. However, current DC-link converters using other modulation schemes, e.g., conventional SVPWM (see **Appendix D**), can potentially generate comparable CM pre-filter noise as voltage DC-link converters.

voltage DC-link topology for most operating points.

#### V. CONCLUSION

This paper presents a generic comparison of three-phase voltage and current DC-link converters (rectifiers or inverters) with regard to DM and CM pre-filter EMI n oise emissions. The comparison is enabled by simplified a nalytical models for the envelopes of the DM and CM pre-filter noise emission amplitude spectra, whose accuracy is confirmed by experimental verification with 10 kW, 400 V (line-to-line rms) current DC-link and voltage DC-link demonstrator systems. For DM, the current DC-link converter shows lower pre-filter noise emissions if the equivalent AC resistance it represents to the mains is higher than the LISN's  $50-\Omega$  measurement resistor, i.e., for lower power level and/or higher mains voltages. In contrast, the current DC-link converter features significantly lower CM pre-filter noise emissions, in typical cases, which makes it an interesting option for motor drive inverters.

#### APPENDIX A - VOLTAGE DC-LINK SVPWM

In the following, first, t he S VPWM of v oltage DC-link converters [13], [14] is briefly described, including a detailed explanation of the switching sequence within the selected  $60^{\circ}$ -sector of one mains period ( $v_a > v_b > v_c$ , see **Fig. 1b**), along with the DM and CM noise voltages associated with each switching state. Subsequently, comprehensive derivations of (6) and (8) in **Section II-A** are also provided.

## I. Voltage DC-Link SVPWM

The switching state of a two-level 3-Φ voltage DC-link PFC rectifier involves the  $3-\Phi$  switching states, typically formed by three two-level bridge legs. This results in a total of six active and two zero voltage space vectors (SVs) (see Fig. 1b). As an example, the active switching state [100] denotes that the phase-a bridge leg connects to the high-side DC-link rail p by turning  $T_{a,h}$  on and the other two phase (phase b and c) bridge legs connect to the low-side DC-link rail n by activating  $T_{b,l}$ and T<sub>c.1</sub>. When all three phase bridge legs are connected to the same side of the DC-link, e.g., to the high-side [111] or to the low-side [000], the zero switching state is applied. In these instances, there is no DM voltage, but a relatively large CM voltage is present, i.e.,  $|v_{\rm CM}| = V_{\rm DC}/2$  for zero switching states is larger than  $|v_{\rm CM}| = V_{\rm DC}/6$  for active switching states. **Tab. A.1** lists the switching states for the analyzed two-level 3-Φ voltage DC-link PFC rectifier, and the DM and CM voltages can then be calculated according to (1) and (2).

To synthesize a desired 3- $\Phi$  voltage space vector  $\vec{v}^*$ , each switching period consists of two closest active switching states and two zero switching states. For illustration, a 60°-sector of one mains period ( $v_a > v_b > v_c$ , see **Fig. 1b**) is considered as an example, and a typical symmetric switching sequence, mirrored with respect to the center of a switching period, is applied

$$[000] \rightarrow [100] \rightarrow [110] \rightarrow [111] \rightarrow [110] \rightarrow [100] \rightarrow [000],$$

**TABLE A.1:** Switching states of a two-level  $3-\Phi$  voltage DC-link PFC rectifier using the SVPWM.

| S     | o                | n-sta            | te               | v <sub>DM,a</sub>                          | ν <sub>DM,b</sub> | v <sub>DM,c</sub> | v <sub>CM</sub> |

|-------|------------------|------------------|------------------|--------------------------------------------|-------------------|-------------------|-----------------|

| [000] | T <sub>a,l</sub> | T <sub>b,l</sub> | T <sub>c,l</sub> | 0 V                                        | 0 V               | 0 V               | $-V_{\rm DC}/2$ |

| [111] | T <sub>a,h</sub> | $T_{b,h}$        | $T_{c,h} \\$     | 0 V<br>0 V                                 | $0\mathrm{V}$     | $0\mathrm{V}$     | $+V_{\rm DC}/2$ |

| [100] | T <sub>a,h</sub> | $T_{b,l}$        | $T_{c,l}$        | $+2V_{DC}/3$<br>$+V_{DC}/3$<br>$-V_{DC}/3$ | $-V_{\rm DC}/3$   | $-V_{\rm DC}/3$   | $-V_{\rm DC}/6$ |

| [110] | T <sub>a,h</sub> | $T_{b,h}$        | $T_{c,l} \\$     | $+V_{DC}/3$                                | $+V_{\rm DC}/3$   | $-2V_{\rm DC}/3$  | $+V_{\rm DC}/6$ |

| [010] | T <sub>a,l</sub> | $T_{b,h}$        | $T_{c,l}$        | $-V_{\rm DC}/3$                            | $+2V_{\rm DC}/3$  | $-V_{\rm DC}/3$   | $-V_{\rm DC}/6$ |

| [011] | T <sub>a,l</sub> | $T_{b,h}$        | $T_{c,h} \\$     | $-2V_{\rm DC}/3$                           | $+V_{\rm DC}/3$   | $+V_{\rm DC}/3$   | $+V_{\rm DC}/6$ |

| [001] | T <sub>a,l</sub> | $T_{b,l}$        | $T_{c,h} \\$     | $-V_{\rm DC}/3$                            | $-V_{\rm DC}/3$   | $+2V_{\rm DC}/3$  | $-V_{\rm DC}/6$ |

| [101] | T <sub>a,h</sub> | $T_{b,l}$        | $T_{c,h} \\$     | $-2V_{DC}/3$ $-V_{DC}/3$ $+V_{DC}/3$       | $-2V_{\rm DC}/3$  | $+V_{\rm DC}/3$   | $+V_{\rm DC}/6$ |

with the generated DM voltage of phase a

$$0 \text{ V} \rightarrow 2V_{DC}/3 \rightarrow V_{DC}/3 \rightarrow 0 \text{ V} \rightarrow V_{DC}/3 \rightarrow 2V_{DC}/3 \rightarrow 0 \text{ V}$$

.

and the CM voltage

$$-V_{\rm DC}/2 \rightarrow -V_{\rm DC}/6 \rightarrow V_{\rm DC}/6 \rightarrow V_{\rm DC}/2 \rightarrow V_{\rm DC}/6 \rightarrow -V_{\rm DC}/6 \rightarrow -V_{\rm DC}/2.$$

#### II. DM & CM Noise Source Derivation

The duty cycles of three-phase bridge legs at the mains angle  $\varphi$  are

$$\begin{split} d_{\rm a}(\varphi) &= 1/2 + [v_{\rm a}(\varphi) + v_{\rm CM,LF}(\varphi)]/V_{\rm DC}, \\ d_{\rm b}(\varphi) &= 1/2 + [v_{\rm b}(\varphi) + v_{\rm CM,LF}(\varphi)]/V_{\rm DC}, \\ d_{\rm c}(\varphi) &= 1/2 + [v_{\rm c}(\varphi) + v_{\rm CM,LF}(\varphi)]/V_{\rm DC}, \end{split} \tag{A.1}$$

and in the considered  $60^{\circ}$ -sector of one mains period ( $v_a > v_b > v_c$ , see **Fig. 1b**), the LF CM injection voltage is

$$v_{\text{CMLF}}(\varphi) = 1/2 \cdot v_{\text{b}}(\varphi)$$

(A.2)

if using the standard voltage DC-link SVPWM [13], [14]. Thus, the dwell times of switching states can be derived from the obtained duty cycles of bridge legs. [000] is the only switching state where low-side switch  $T_{a,l}$  of phase a is turned on, over one switching period, and therefore,

$$\delta_{000}(\varphi) = 1 - d_{\mathbf{a}}(\varphi). \tag{A.3}$$

The same philosophy is applied to another zero-switching state [111], which is the only state with the on-state of  $T_{c,h}$  over one switching period

$$\delta_{111}(\varphi) = d_{\rm c}(\varphi). \tag{A.4}$$

Then, the duty cycle of phase-b bridge leg is applied to calculate the dwell times of the other two active switching states as

$$\delta_{110}(\varphi) = d_{b}(\varphi) - d_{c}(\varphi),$$

$$\delta_{100}(\varphi) = d_{a}(\varphi) - d_{b}(\varphi).$$

(A.5)

Based on the obtained dwell times of each switching state, the total CM rms voltage value [see (6) in **Section II-A**] can

be calculated in the considered  $60^{\circ}$ -sector of one mains period as

$$\begin{split} V_{\text{CM,rms}} &= \sqrt{\frac{6}{2\pi} \int_{0}^{\frac{2\pi}{6}} v_{\text{CM,rms}}^{2}(\varphi) \, d\varphi}, \\ &= \sqrt{\frac{6}{2\pi} \int_{0}^{\frac{2\pi}{6}} \left[ (\delta_{100} + \delta_{110}) \cdot \frac{V_{\text{DC}}^{2}}{6^{2}} + (\delta_{111} + \delta_{000}) \cdot \frac{V_{\text{DC}}^{2}}{2^{2}} \right] d\varphi} \\ &= \sqrt{\frac{1}{4} - \frac{\sqrt{3} M_{\text{VDC}}}{3\pi}} \cdot V_{\text{DC}}. \end{split} \tag{A.6}$$

For (8) in **Section II-A**, the rms value of the LF CM noise voltage can be calculated in the considered  $60^{\circ}$ -sector of one mains period as

$$\begin{split} V_{\text{CM,LF,rms}} &= \sqrt{\frac{6}{2\pi} \int_{0}^{\frac{2\pi}{6}} v_{\text{CM,LF}}^{2}(\varphi) \, d\varphi}, \\ &= \sqrt{\frac{6}{2\pi} \int_{0}^{\frac{2\pi}{6}} \left[ \frac{1}{2^{2}} \cdot v_{\text{b}}^{2}(\varphi) \right] d\varphi}, \qquad \text{(A.7) \& (8)} \\ &= \sqrt{\frac{1}{32} - \frac{3\sqrt{3}}{56\pi}} \cdot M_{\text{VDC}} \cdot V_{\text{DC}}, \end{split}$$

### APPENDIX B - CURRENT DC-LINK SVPWM

In the following, first, the reduced CM (RCM) current DC-link SVPWM [27], [31] is briefly described, including a detailed explanation of the switching sequence within the selected  $30^{\circ}$ -sector of one mains period ( $v_{\rm a}>v_{\rm b}>0>v_{\rm c}$ , see Fig. 7b), along with the DM and CM noise currents or voltages associated with each switching state. Subsequently, comprehensive derivations of (15), (18), and (20) in Section III-A are also provided.

## I. Reduced CM (RCM) Current DC-Link SVPWM

The switching states of a current DC-link PFC rectifier can be categorized into active and zero (freewheeling) switching states, which are expressed by the turned-on switches in the high-side and low-side commutation cells. The active switching state [ab] indicates the DC-link current  $I_{\rm DC}$  closing its path through  $T_{\rm a,h}$  and  $T_{\rm b,l}$ , resulting in  $i_{\rm a}^{'}=+I_{\rm DC}$  in phase  $a,\ i_{\rm c}^{'}=-I_{\rm DC}$  in phase  $c,\$ and  $i_{\rm b}^{'}=0$  A in phase b. Eq. (14) provides the CM voltage of the switching state [ab], i.e.,  $(v_{\rm a}+v_{\rm b})/2$ . Moreover, the zero switching state [aa] indicates the DC-link current closing its path through  $T_{\rm a,h}$  and  $T_{\rm a,l}$  resulting in zero DM currents in all three phases, but a CM voltage of  $v_{\rm a}$  is injected. The switching states are summarized in **Tab. B.1**, together with the information on phase DM currents and the generated CM noise voltages.

To synthesize a desired  $3-\Phi$  current space vector  $\vec{i}^*$ , each switching period consists of two closest active switching states and one zero switching state. As an example, we consider a  $30^\circ$ -sector of one mains period  $(v_a > v_b > 0 > v_c)$ , see Fig. 7b), where the active switching states [ac] and [bc] are used and the selection of the zero state ([aa] or [bb] or [cc]) provides a degree of freedom.

**TABLE B.1:** Switching states of a 3- $\Phi$  current DC-link PFC rectifier using the RCM SVPWM.

| S    | on-state         |                  | $i_{ m a}^{'}$ | $i_{ m b}^{'}$     | $i_{ m c}^{'}$     | v <sub>pk</sub> | $v_{nk}$    | ν <sub>CM</sub>                                                                                                                                                 |

|------|------------------|------------------|----------------|--------------------|--------------------|-----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [aa] | T <sub>a,h</sub> | T <sub>a,l</sub> | 0 A            | 0 A                | 0 A                | v <sub>a</sub>  | $v_{\rm a}$ | $v_{\mathrm{a}}$                                                                                                                                                |

| [bb] | T <sub>b,h</sub> | $T_{b,l}$        | 0 A            | 0 A                | 0 A                | $v_{\rm b}$     | $v_{b}$     | $v_{b}$                                                                                                                                                         |

| [cc] | T <sub>c,h</sub> | $T_{c,l} \\$     | 0 A            | 0 A                | 0 A                | $v_{\rm c}$     | $v_{\rm c}$ | $egin{aligned} v_{ m a} \ v_{ m b} \ v_{ m c} \end{aligned}$                                                                                                    |

| [ab] | T <sub>a,h</sub> | $T_{b,l}$        | $+I_{ m DC}$   | $-I_{ m DC}$       | 0 A                | $v_{\rm a}$     | $v_{b}$     | $ \frac{(v_a + v_b)/2}{(v_a + v_b)/2} $ $ \frac{(v_b + v_c)/2}{(v_b + v_c)/2} $ $ \frac{(v_b + v_c)/2}{(v_a + v_c)/2} $ $ \frac{(v_a + v_c)/2}{(v_a + v_c)/2} $ |

| [ba] | T <sub>b,h</sub> | $T_{a,l} \\$     | $-I_{ m DC}$   | $+I_{\mathrm{DC}}$ | 0 A                | $v_{\rm b}$     | $v_{\rm a}$ | $(v_{\mathrm{a}}\!+\!v_{\mathrm{b}})\big/2$                                                                                                                     |

| [bc] | T <sub>b,h</sub> | $T_{c,l}$        | 0 A            | $+I_{\mathrm{DC}}$ | $-I_{\mathrm{DC}}$ | $v_{\rm b}$     | $v_{\rm c}$ | $(v_{\mathrm{b}}\!+\!v_{\mathrm{c}})\big/2$                                                                                                                     |

| [cb] | T <sub>c,h</sub> | $T_{b,l}$        | 0 A            | $-I_{\mathrm{DC}}$ | $+I_{\mathrm{DC}}$ | $v_{\rm c}$     | $v_{b}$     | $(v_{\mathrm{b}}\!+\!v_{\mathrm{c}})\!\big/\!2$                                                                                                                 |

| [ca] | T <sub>c,h</sub> | $T_{a,l} \\$     | $-I_{ m DC}$   | 0 A                | $+I_{\mathrm{DC}}$ | $v_{\rm c}$     | $v_{\rm a}$ | $(v_a+v_c)/2$                                                                                                                                                   |

| [ac] | T <sub>a,h</sub> | $T_{c,l}$        | $+I_{ m DC}$   | 0 A                | $-I_{\mathrm{DC}}$ | $v_a$           | $v_{\rm c}$ | $(v_{\mathrm{a}}\!+\!v_{\mathrm{c}})\big/2$                                                                                                                     |

In this paper, the zero state is determined by the phase with the minimum voltage, i.e., phase b in the analyzed sector. This modulation scheme is made to achieve a reduced CM voltage without sacrificing switching losses, a technique known as RCM SVPWM [27]. Importantly, this method also advantageously facilitates the integrated CM filter by ensuring a continuous LF CM voltage without any voltage step at the sector boundary. Thus, considering one switching period in the analyzed sector (see **Fig. 8**), the switching sequence is

$$[bb] \rightarrow [bc] \rightarrow [ac] \rightarrow [bc] \rightarrow [bb],$$

the DM current noise of phase a is

$$0 A \rightarrow 0 A \rightarrow I_{DC} \rightarrow 0 A \rightarrow 0 A$$

and the generated CM voltage is

$$v_{\rm b} \to (v_{\rm b} + v_{\rm c})/2 \to (v_{\rm a} + v_{\rm c})/2 \to (v_{\rm b} + v_{\rm c})/2 \to v_{\rm b}$$

.

Note that, for the PFC operation, CM voltages of the active switching states and the zero switching states have the opposite sign, e.g., in the selected sector where  $v_a > v_b > 0 > v_c$

$$v_{\rm b} > 0 > (v_{\rm a} + v_{\rm c})/2 > (v_{\rm b} + v_{\rm c})/2$$

is obtained. This explains the shape of  $V_{\text{CM,LF,rms}}$  exhibiting a turning point, where it transitions from a descending to an ascending slope (see **Fig. 10a**).

#### II. DM & CM Noise Source Derivation

The 3- $\Phi$  duty cycles at the mains angle  $\varphi$  are:

$$\begin{split} d_{\rm a}(\varphi) &= |i_{\rm a}(\varphi)|/I_{\rm DC} = M_{\rm CDC} \cdot |\cos(\varphi)|, \\ d_{\rm b}(\varphi) &= |i_{\rm b}(\varphi)|/I_{\rm DC} = M_{\rm CDC} \cdot |\cos(\varphi - 2/3\pi)|, \\ d_{\rm c}(\varphi) &= |i_{\rm c}(\varphi)|/I_{\rm DC} = M_{\rm CDC} \cdot |\cos(\varphi + 2/3\pi)|, \end{split} \tag{B.1}$$

and in the selected  $30^{\circ}$ -sector of one mains period ( $v_{\rm a} > v_{\rm b} > 0 > v_{\rm c}$ , see Fig. 7b), dwell time of three switching states are

$$\begin{split} &\delta_{\rm ac}(\varphi) = d_{\rm a}(\varphi), \\ &\delta_{\rm bc}(\varphi) = d_{\rm b}(\varphi), \\ &\delta_{\rm bb}(\varphi) = 1 - d_{\rm a}(\varphi) - d_{\rm b}(\varphi). \end{split} \tag{B.2}$$

Based on the obtained dwell times of each switching state, the total DM rms current value [see (15) in **Section III-A**] can be calculated considering quarter-wave symmetry within one mains period as

$$\begin{split} I_{\text{DM,rms}} &= i_{\text{a,rms}}^{'} = \sqrt{\frac{2}{\pi} \int_{0}^{\frac{\pi}{2}} \left[ d_{\text{a}}(\varphi) \cdot I_{\text{DC}}^{2} \right] d\varphi}, \\ &= \sqrt{\frac{2}{\pi} M_{\text{CDC}} \cdot I_{\text{DC}}^{2} \cdot \int_{0}^{\frac{\pi}{2}} \cos(\varphi) d\varphi}, \\ &= \sqrt{\frac{2M_{\text{CDC}}}{\pi}} \cdot I_{\text{DC}}. \end{split} \tag{B.3) & (15)}$$

For (18) in **Section III-A**, the total DM rms current value can be calculated over the selected 30°-sector as

$$V_{\text{CM,rms}} = \sqrt{\frac{6}{\pi}} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} v_{\text{CM,rms}}^{2}(\varphi) d\varphi,$$

$$= \sqrt{\frac{6}{\pi}} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} [\delta_{\text{ac}} \cdot (\frac{v_{\text{a}} + v_{\text{c}}}{2})^{2} + \delta_{\text{bc}} \cdot (\frac{v_{\text{b}} + v_{\text{c}}}{2})^{2} + \delta_{\text{bb}} \cdot v_{\text{b}}^{2}] d\varphi,$$

$$= \sqrt{\frac{8\sqrt{3} - 15}{8\pi}} M_{\text{CDC}} + \frac{2\pi - 3\sqrt{3}}{4\pi} \cdot V_{\text{ph,pk}}.$$

(B.4) & (18)

For (20) in **Section III-A**, the rms value of LF CM voltage over the selected 30°-sector (same as over one mains period) becomes

$$\begin{split} V_{\text{CM,LF,rms}} &= \sqrt{\frac{6}{\pi}} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} v_{\text{CM,LF}}^{2}(\varphi) \, d\varphi, \\ &= \sqrt{\frac{6}{\pi}} \int_{\frac{\pi}{6}}^{\frac{\pi}{3}} [\delta_{\text{ac}} \cdot (\frac{v_{\text{a}} + v_{\text{c}}}{2}) + \delta_{\text{bc}} \cdot (\frac{v_{\text{b}} + v_{\text{c}}}{2}) + \delta_{\text{bb}} \cdot v_{\text{b}}]^{2} \, d\varphi, \\ &= \sqrt{\frac{2\pi - 3\sqrt{3}}{4\pi}} - \frac{\sqrt{3}}{2\pi} M_{\text{CDC}} + \frac{12\pi - 9\sqrt{3}}{32\pi} M_{\text{CDC}}^{2} \cdot V_{\text{ph,pk}}. \end{split}$$

$$(B.5) \& (20)$$

# APPENDIX C - PRE-FILTER NOISE ENVELOPES OF OTHER VOLTAGE DC-LINK PWMS

This Appendix analyzes the applicability of the lowcomplexity analytical pre-filter noise envelopes from (11) for DM and (12) for CM noise emissions, which are derived in Section II-A, to the voltage DC-link converter modulated by PWM schemes other than the standard SVPWM. A discontinuous SVPWM (DPWM) is taken as an example, where the phase with the maximum absolute voltage is always clamped (i.e., the corresponding half-bridge is not switched during the corresponding interval), and, accordingly, either [111] or [000] is selected as the zero state within a given switching period. To synthesize a desired voltage space vector  $\vec{v}^*$ , the switching state sequence of each switching period is composed of the two closest active switching states and one zero switching state. For illustration, a 60°-sector of one mains period where phase c retains the minimum phase voltage is considered as an example, and a typical symmetric switching sequence,

Fig. 15: Simulated key waveforms (with a zoomed view over one switching period) of the two-level 3- $\Phi$  voltage DC-link PFC rectifier (see Fig. 1a) operating with a 400 V (line-to-line rms) mains, 800 V DC-link and/or output voltage, and 10 kW output power using discontinuous SVPWM (DPWM). Taking phase c as an example, (a) shows the switching stage phase voltage  $v_{c'o}$ , which can be decomposed into (b) DM and (e) CM components. Furthermore, (c) and (f) show the DM and CM HF noise voltages (i.e., the prefilter DM and CM noise emissions). Note that the phase with the maximum absolute voltage, i.e., phase c in the selected sector, is clamped during the entire sector, which is achieved by a suitable LF CM injection  $v_{\text{CM,LF}}$ , and hence the corresponding bridge leg is not switching within the switching period (only the first half of one switching period is shown in the zoomed view due to the switching sequence symmetry).

mirrored with respect to the center of a switching period, is applied:

$$[000] \rightarrow [100] \rightarrow [110] \rightarrow [110] \rightarrow [100] \rightarrow [000].$$

In the selected sector, phase c bridge leg is always connected to the low-side DC rail n during one switching period, as only [000] (see **Fig. 15**, and not also [111] as in conventional SVPWM shown in **Fig. 2**) is applied as the zero state.

The analytical envelopes derived for the conventional SVPWM (see (7) and (10) in **Section II-A**) are first applied to estimate the amplitude spectra of the simulated  $v_{\rm DM,HF}$  and  $v_{\rm CM,HF}$  using the DPWM as shown in **Fig. 16**. Excellent agreement between the analytical envelopes and the simulated amplitude spectra can be observed for the exemplary modulation indices of  $M_{\rm VDC}=0.8$  and  $M_{\rm VDC}=1.0$ . This can be explained with **Fig. 4**, where, regardless of  $M_{\rm VDC}$ ,  $V_{\rm CM,LF,rms}$  always contributes a small part and  $V_{\rm CM,LF,rms}^2$  is even too small to get noticed. Therefore, without losing accuracy, the analytical envelopes from (7) and (10) can be directly applied to voltage DC-link converters modulated by other PWM schemes, i.e., with different injected LF CM voltages.

Furthermore, to highlight the generality of the modeling method proposed in [24] and utilized herein, the low-complexity analytical expressions for the pre-filter noise envelopes resulting for DPWM shown in **Fig. 15** are specifically

**Fig. 16:** DM (top row) and CM (bottom row) pre-filter noise amplitude spectra (the black solid lines indicate the envelopes of the measured spectra) extracted from circuit simulations of a  $10\,\mathrm{kW}$  two-level  $3\text{-}\Phi$  voltage DC-link PFC rectifier modulated by DPWM. The rectifier interfaces a  $400\,\mathrm{V}$  mains using different DC-link voltages  $V_{\mathrm{DC}}$  (different modulation indices  $M_{\mathrm{VDC}}$ ) and a switching frequency of  $f_{\mathrm{sw}}=100\,\mathrm{kHz}$ . The envelopes are obtained with the low-complexity analytical expressions (11) for DM and (12) for CM, respectively. Note that the dashed lines represent the analytical pre-filter noise envelopes derived in **Section II-A**, which are grouped by colors according to the respective operating points. As a comparison, the CM noise envelopes specifically derived for the DPWM in **Appendix C** are shown in red solid lines; the DM noise envelopes are identical for both PWM schemes.

derived hereafter. Since the difference between the considered DPWM and the standard SVPWM only lies in the relative shares of two zero states ([000] and [111]),  $V_{\text{a'o,rms}}$  in (3),  $V_{\text{DM,LF,rms}}$  in (4),  $V_{\text{CM,rms}}$  in (6), and  $V_{\text{DM,HF,rms}}$  in (7) remain as derived in **Section II-A**. A CM voltage

$$v_{\text{CM,LF}}(\varphi) = -\frac{1}{2}V_{\text{DC}} - v_{\text{c}}(\varphi), \qquad (C.1)$$

is injected to ensure that phase c bridge leg is always connected to the low-side DC rail n in the selected sector, and thus.

$$V_{\text{CM,LF,rms}} = \sqrt{\frac{3}{\pi} \int_{\frac{6}{\pi}}^{\frac{\pi}{2}} v_{\text{CM,LF}}^{2}(\varphi) \, d\varphi},$$

$$= \sqrt{\frac{1}{4} - \frac{3}{2\pi} M_{\text{VDC}} + \frac{2\pi + 3\sqrt{3}}{16\pi} M_{\text{VDC}}^{2}} \cdot V_{\text{DC}}.$$

(C.2)

Then, the rms value of the HF CM noise voltage is

$$\begin{split} V_{\rm CM,HF,rms} &= \sqrt{V_{\rm CM,rms}^2 - V_{\rm CM,LF,rms}^2}, \\ &= \sqrt{\frac{9 - 2\sqrt{3}}{6\pi} M_{\rm VDC} - \frac{3\sqrt{3} + 2\pi}{16\pi} M_{\rm VDC}^2} \cdot V_{\rm DC}. \end{split}$$

(C.3

**Fig. 16** shows the obtained envelopes (red solid lines) and compares them against the analytical envelopes using (10), resulting in a negligible difference.

Fig. 17: Simulated key waveforms (with a zoomed view over one switching period) of the 3- $\Phi$  current DC-link PFC rectifier (see Fig. 7a) operating with the conventional SVPWM, i.e., using the phase with the maximum absolute voltage as the zero state instead of the phase with the minimum absolute voltage in the RCM SPWM (see Fig. 8), from a 400 V (line-to-line rms) mains with 400 V DC output voltage, 10 kW output power, and a DC-link current of 25 A. Taking phase a as an example, (a) shows the total DM input current  $i_a$  and (b) its HF component  $i_{\rm DM,HF}$ ; (c) shows the total CM noise voltage  $v_{\rm CM}$  and (d) its HF component  $v_{\rm CM,HF}$ .

# APPENDIX D - PRE-FILTER NOISE ENVELOPES OF OTHER CURRENT DC-LINK PWMS

This Appendix analyzes the applicability of the derived low-complexity analytical pre-filter noise envelopes from (16) for DM and (21) for CM noise emissions to other current DC-link PWM schemes. The conventional current DC-link SVPWM is selected as a representative example, which generates the same DM but higher CM noise emissions compared to the reduced-CM (RCM) SVPWM considered in **Section III-A**.

To synthesize a desired current space vector  $\vec{i}^*$ , the switching state sequence of each switching period is composed of the two closest active switching states and one zero switching state. As an example, we consider a 30°-sector of one mains period  $(v_a > v_b > 0 > v_c$ , see **Fig. 7b**), where the same active switching states [ac] and [bc] are used as in the RCM SVPWM but the zero state [cc] instead of [bb] is selected in the conventional SVPWM. Thus, considering one switching period in the analyzed sector (see **Fig. 7b**), the switching sequence is

$$[cc] \rightarrow [bc] \rightarrow [ac] \rightarrow [bc] \rightarrow [cc].$$

The selection of the zero states has no impact on the total DM input current  $i_{\rm a'}$  and its HF component  $i_{\rm DM,HF}$  (cf. **Fig. 8** and **Fig. 17**). Thus,  $I_{\rm DM,rms}$  in (15), and  $I_{\rm DM,HF,rms}$  in (16) derived in **Section III-A** can be directly applied, and the same holds for the DM pre-filter noise envelopes (see **Fig. 18**). For CM components, since the zero state is the main contributor to the CM noise emission in the current DC-link converter, the rms CM voltage of one switching period  $v_{\rm CM,rms}(\varphi)$  at a

Fig. 18: DM (top row) and CM (bottom row) pre-filter noise amplitude spectra (the black solid lines indicate the envelopes of the measured spectra) extracted from circuit simulations of a  $10\,\mathrm{kW}$   $3\text{-}\Phi$  current DC-link PFC rectifier modulated by the conventional SVPWM. The rectifier interfaces a  $400\,\mathrm{V}$  mains using a switching frequency of  $100\,\mathrm{kHz}$  with different modulation indices  $M_{\mathrm{CDC}}$  (i.e., different power levels). The envelopes (dashed) are obtained with the low-complexity analytical expressions (16) for DM and (21) for CM, respectively as derived in Section III-A for the RCM SVPWM, which are grouped by colors according to the respective operating points. As a comparison, the CM noise envelopes specifically derived for the conventional SVPWM in Appendix D are shown as red solid lines; the DM noise envelopes are identical for both PWM schemes.

mains angle  $\varphi$  has to be recalculated as