© 2025 IEEE

IEEE Transactions on Power Electronics (Early Access)

### Synergetic Control of a Monolithic-Bidirectional-GaN-Transistor-Based Three-Phase Current DC-Link AC-AC Converter

- N. Nain,

- D. Zhang,

- J. W. Kolar,

- J. Huber

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works

# Synergetic Control of a Monolithic-Bidirectional-GaN-Transistor-Based Three-Phase Current DC-Link AC-AC Converter

Neha Nain, Daifei Zhang, *Member, IEEE*, Johann W. Kolar, *Fellow, IEEE*, and Jonas Huber, *Senior Member, IEEE*

Abstract-Variable speed drives (VSDs) operating from a three-phase mains are typically realized as ac-ac voltage dclink/source converters (VSCs). However, compact VSC-based VSDs implemented with wide-bandgap (WBG) semiconductors such as SiC and GaN often require LC output filters to protect the motor from high dv/dt of the switched voltage. In contrast, ac-ac current dc-link/source converters (CSCs) featuring a back-to-back connection of a current-source rectifier (CSR) and current-source inverter (CSI) with a shared dc-link inductor inherently provide continuous motor voltages, making them an interesting alternative. Therefore, this paper first introduces the loss-optimal operating mode of an ac-ac CSC: using the minimum possible and hence time-varying dc-link current (defined by the maximum absolute value of CSR's and the CSI's phase currents), the conduction losses are minimized and either the CSR or the CSI operates with 2/3-PWM, i.e., at any given time, one phase terminal is clamped to the dc-link inductor while PWM is only needed to synthesize the remaining two phase currents, thus reducing switching losses. The respective other stage employs PWM in all three phases (3/3-PWM) and shapes the dc-link current. Closed-form expressions for the transistor conduction and switching losses facilitate a quantitative assessment of the efficiency improvements. Then, the paper proposes a synergetic control method that realizes lossoptimal operation for the entire output voltage and current range of the ac-ac CSC, with motor voltages lower and higher than the grid voltage, and ensures smooth transitions between operating points. Finally, detailed experimental results of a 1.4 kW, 200 V (line-to-line rms) ac-ac CSC demonstrator using first-generation 600 V, 140 m $\Omega$  monolithic bidirectional GaN transistors, gridside and motor-side EMI filters, and a switching frequency of 72 kHz confirm the loss optimal operation and seamless transitions between operating points. Compared to conventional operation and in close alignment with calculation results, the measured nominal ac-ac efficiency increases by 0.3% to 97% with the proposed loss-optimal operation, and part-load efficiency gains of up to 1% are observed.

#### I. Introduction

Electric motor applications account for an estimated share of about 45% of the global electricity consumption [1]. Driven by the trends towards urbanization and ubiquitous automation, the demand for electric motor drive systems is expected to increase further [2]. Therefore, any investment towards improving the efficiency of motor-driven systems and/or thus reducing their over-all energy consumption is of utmost importance. Variable speed drive (VSD) systems enable significant energy savings in motor-driven applications, particularly for systems operating with variable load [1]–[6].

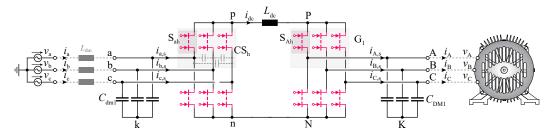

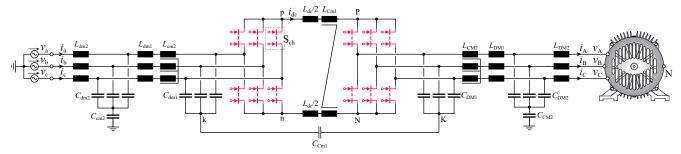

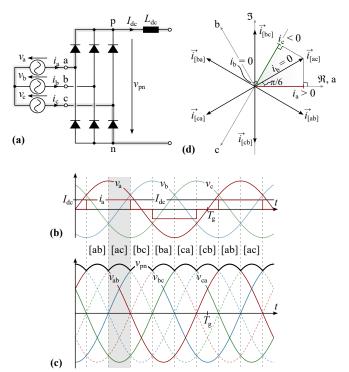

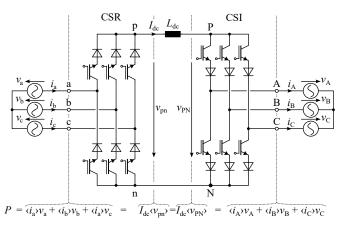

In typical applications, VSDs are supplied from a three-phase ac mains, i.e., are ac-ac power converters which are realized as a back-to-back connection of an ac-dc rectifier and a dc-ac inverter power stage. The two converter stages are coupled with a common intermediate energy storage element which can either be a dc-link capacitor (voltage-source converter, VSC) or a dc-link inductor (current-source converter, CSC) as shown in **Fig. 1**. The CSC consists of a grid-side current-source rectifier (CSR) and motor-side current-source inverter (CSI) that share a common dc-link inductor.

VSCs require semiconductor devices with only unipolar voltage blocking but bidirectional current conduction capability, whereas CSCs require bipolar-voltage-blocking devices with only unidirectional current conduction capability<sup>1</sup>. Thus, in the past, CSCs have been implemented with thyristors, GTOs and GCTs for high power applications where they were preferred over VSCs due to absence of large electrolytic capacitor

$N.\ Nain,\ D.\ Zhang,\ J.\ W.\ Kolar,\ and\ J.\ Huber are with the Power Electronic Systems Laboratory, ETH Zurich, Switzerland.$

<sup>1</sup>If a reversal of the polarity of the dc-side voltages of the rectifier and inverter stages is allowed for power regeneration from the load to the grid

Fig. 1. Core structure of the power circuit of the considered ac-ac current-source converter (CSC), which is formed by a back-to-back arrangement of a current-source rectifier (CSR) and a current-source inverter (CSI), both employing monolithic bidirectional switches (M-BDSs); specifically, the employed first generation  $600\,V$ ,  $140\,m\Omega$  GaN M-BDSs facilitate interfacing a  $200\,V$  (line-to-line rms) three-phase ac mains. The dashed rectangle labeled  $CS_h$  indicates an exemplary commutation cell of the CSR, which consists of three M-BDSs and three delta-connected commutation capacitors. Note that the grid-side and motor-side EMI filter stages, that are employed in the finally built hardware demonstrator (cf. Section IV), are not shown here for the sake of clarity and the missing relevance for the proposed synergetic control method.

[7], [8], the capability of four-quadrant operation (supporting regenerative braking of the motor) by allowing reversal of the dc-side voltage polarity to reverse power flow without requiring extra components, smooth motor voltages, and inherent load short-circuit protection due to large dc-link inductor limiting the di/dt of the short circuit current [9]–[11].

CSCs have also been considered for low-power applications already more than two decades ago, realizing the bipolar-voltage-blocking device as a series connection of an IGBT and a diode or with reverse blocking IGBTs [12]–[14]. However, with switching frequencies thus limited to typically less than 16 kHz, the notion of a bulky dc-link inductor has emerged. But, as CSCs offer some key advantages including, but not limited to, inherently providing smooth output voltages to the motor without needing a dedicated LC filter, research towards CSCs with higher switching frequencies and hence compact dc-link inductors has continued, also driven by wide-bandgap (WBG) power semiconductors [15]–[22].

It should also be noted that the use of CSCs has not been limited to motor drive systems; CSCs have been and are still considered for a wide range of other applications such as data center power supplies [23]–[25], solid-state transformers [26], grid interfaces for renewable energy [27] and EV chargers [28], [29].

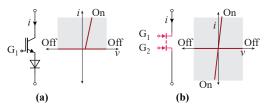

Until recently, the only way of implementing switching devices with bipolar voltage-blocking and bidirectional currentconducting capability (bidirectional switch, BDS, sometimes also called ac switch) for CSCs was an inverse-series connection of two transistors (or a transistor and a diode in applications where unidirectional current flow suffices). Both devices must be rated for the full blocking voltage to ensure the required bipolar voltage blocking capability. Consequently, the on-state resistance of such a series arrangement is twice that of a single transistor. The corresponding increase in conduction losses can be avoided by connecting a parallel branch of yet another inverse-series combination of two transistors, resulting in a BDS with the same on-state resistance as a single transistor but with four times the semiconductor chip area [30]. To address this clear drawback of CSCs compared to VSCs, there has been continuing research towards developing monolithic BDSs (M-BDSs) that realize a factor-of-four reduction of chip area, i.e., provide BDS functionality with the same on-state resistance and the same chip area as a unipolar voltage blocking device (the same drift region is used for blocking voltages of both polarities) [31]-[38]. By now, there are mature M-BDSs using GaN technology; specifically,  $600 \,\mathrm{V}$ ,  $140 \,\mathrm{m}\Omega$  devices [39] are available and have been characterized by the authors for application in CSCs [40], [41] and T-type VSC rectifiers [42]. Therefore, GaN M-BDSs are shown as switching devices<sup>2</sup> in Fig. 1, which depicts the core stage of the considered ac-ac CSC VSD.

VSDs are required to cover wide ranges of output voltage

<sup>2</sup>The depiction of GaN M-BDSs in this paper illustrates that both gates are normally-off, as indicated by two discontinuities in the connection between the two source terminals. Note that the use of dual-gate M-BDSs in CSC based VSDs also requires the implementation of multi-step commutation strategy similar to the BDS implemented with inverse-series connection of two transistors.

TABLE I

KEY SPECIFICATIONS OF THE CONSIDERED AC-AC CSC.

| Parameter                            |                    | Value | Unit |

|--------------------------------------|--------------------|-------|------|

| Rated power                          | $P_{\rm n}$        | 1.4   | kW   |

| Grid line-to-line RMS voltage        | $V_{\rm g,n}$      | 200   | V    |

| Grid frequency                       | $f_{\mathrm{g}}$   | 50    | Hz   |

| Nom. motor phase current             | $I_{\mathrm{m,n}}$ | 4     | A    |

| Nom. motor line-to-line RMS voltage  | $V_{ m m,n}$       | 200   | V    |

| Max. motor line-to-line peak voltage | $\hat{V}_{ m m,m}$ | 400   | V    |

| Max. motor frequency                 | $f_{ m m}$         | 200   | Hz   |

Note: Capital V denote line-to-line RMS voltages, capital I denote phase RMS currents and subscript g and m denote a grid and motor side quantity respectively.

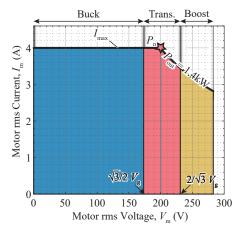

**Fig. 2.** Output voltage/current operating area of the ac-ac CSC from **Fig. 1** with specifications from **Tab. I**, where the buck, transition, and boost regions are indicated. For motor voltages above the nominal value of  $V_{\rm m}=200\,{\rm V}$ , the power rating of the CSR limits the maximum motor current (Given the fixed grid voltage, the rated power of 1.4 kW limits the maximum grid side current which results in lower current at the motor side for motor voltages higher than the nominal value of  $V_{\rm m}=200\,{\rm V}$ .). The current/power ratings follow from available first-generation 600 V, 140 mΩ GaN M-BDSs, and target switching frequency of  $f_{\rm s}=72\,{\rm kHz}$  [41].

(proportional to the motor speed) and current (proportional to the motor torque) as indicated in Fig. 2 for the ac-ac CSC system from Fig. 1 with specifications listed in Tab. I. The 600 V blocking voltage of available GaN M-BDSs facilitates operation from a 200 V three-phase mains as used in the U.S. or in Japan. The wide output voltage range implies that the VSD must feature both, buck and boost capability as highlighted in Fig. 2. Pure buck operation occurs if the instantaneous maximum of the absolute motor voltages  $v_A$ ,  $v_B$  and  $v_C$  is lower than the instantaneous maximum of the absolute three phase input voltages  $v_a$ ,  $v_b$  and  $v_c$ , i.e., if  $V_m < \sqrt{3}/2 \cdot V_g$  with  $V_m$  and  $V_{\rm g}$  denoting the motor and mains line-to-line rms voltages. In analogy, pure boost operation occurs if  $V_{\rm m} > 2/\sqrt{3} \cdot V_{\rm g}$ . Between these two boundaries, the CSC operates in the transition region, i.e., changes sequentially between instantaneous boost and buck operation. Note that for high motor voltages of  $V_{\rm m} > 200 \, \rm V$ , the maximum motor current (motor power) is limited by the CSR's rated power of  $P_n = 1.4 \,\mathrm{kW}$ . Please refer to **Appendix A** for a brief overview on the operating principle of CSCs.

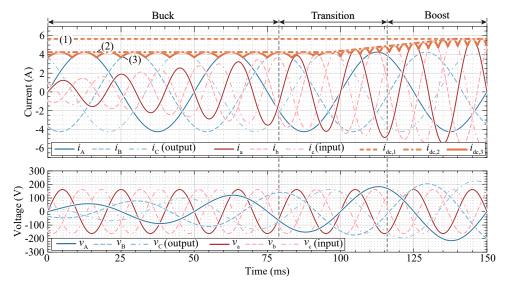

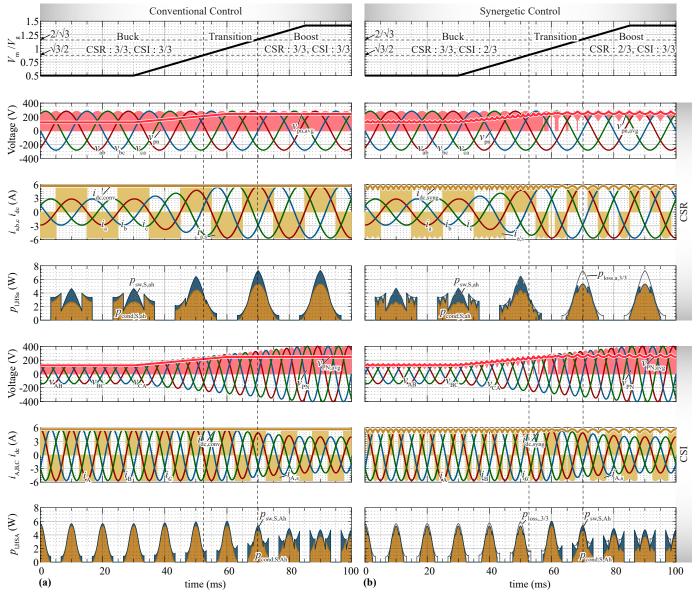

Fig. 3 illustrates the phase current and voltage waveforms on the grid and the motor side of the ac-ac CSC during buck, transition, and boost mode for constant output current amplitude

Fig. 3. Options for selecting the dc-link current  $i_{dc}$  in an ac-ac CSC operating with constant amplitudes of the output/motor currents  $i_A$ ,  $i_B$ ,  $i_C$  but increasing amplitudes of the output phase voltages  $v_A$ ,  $v_B$ ,  $v_C$ , i.e., increasing output power. Thus, the constant amplitudes of the mains voltages  $v_a$ ,  $v_b$ ,  $v_c$  imply increasing amplitudes of the mains currents  $i_a$ ,  $i_b$ ,  $i_c$  such that the input/output power balance is maintained (see also the **Appendix**). Note that in a motor application, an increase of the output/motor voltage is coupled to an increase of the output frequency; this increase in frequency is, however, not important for the explanation of the proposed synergetic control method and therefore not shown for the sake of better visibility. (1) Non-adaptive constant dc-link current at a level high enough for all operating points. (2) Adaptive constant dc-link current equal to the amplitude of the mains or motor phase currents (determined by the larger of the two) at a given operating point. (3) Variable dc-link current / synergetic control [40], where the dc-link current equals the instantaneous maximum of the absolute values of the grid and motor phase currents.

while the load voltage amplitudes increase over time (note that for a motor load, increasing output/motor voltage is coupled with increasing frequency; however, the increase in frequency is not shown in the figure for the sake of clarity and better visibility). Because of the thus increasing motor power and the fixed grid voltage  $V_{\rm g} = 200\,{\rm V}$ , the grid currents increase, too, to maintain the input-output power balance.

In ac-ac CSC systems, generally the CSR controls the dc-link current  $i_{\rm dc}$  to a reference value while the CSI modulates  $i_{\rm dc}$  to synthesize the required ac output currents [8], [12], [16], [23], [43], [44]. There are three options for selecting the dc-link current reference.

1) Non-adaptive constant dc-link current: The standard method, which is straightforward to implement, employs a single, constant  $i_{\rm dc}$  throughout the operating range [16], [45], analogous to maintaining a constant dc-link voltage in ac-ac VSC systems. The modulation indices for the CSR and the CSI are:

$$m_{\rm g} = \hat{i}_{\rm g}/i_{\rm dc}, \quad m_{\rm m} = \hat{i}_{\rm m}/i_{\rm dc},$$

(1)

respectively, where,  $\hat{i}_g$  and  $\hat{i}_m$  are the amplitudes of the local average values of the CSR's and the CSI's ac-side currents  $(i_{a,s}$  for CSR's phase a and  $i_{A,s}$  for CSI's phase A in **Fig. 1**). Since both,  $m_g, m_m \in [0,1]$ ,  $i_{dc}$  must be at least equal to max  $\{\hat{i}_{g,max}, \hat{i}_{m,max}\}$ , where  $\hat{i}_{g,max}$  and  $\hat{i}_{m,max}$  are the maximum amplitudes of  $i_g$  and  $i_m$  in the entire operating range. The curve  $i_{dc,1}$  in **Fig. 3** corresponds to this option.

2) Adaptive constant dc-link current: However, the switching losses of both, the CSR and the CSI, depend directly on  $i_{\rm dc}$ , and at any point in time, overall four M-BDSs as well as the dc-link inductor carry  $i_{\rm dc}$ . Therefore, maintaining the dc-link current at a fixed high value leads to unnecessary high losses for part-load operating points. An alternative method [44] thus

still employs a constant  $i_{dc}$  that is controlled by the CSR, but adapts it for changing load conditions. The minimum constant value of  $i_{dc}$  that is sufficient to cover grid and motor currents at a given operating point,  $\hat{i}_g$  and  $\hat{i}_m$ , is therefore equal to  $i_{dc} = \max{\{\hat{i}_g, \hat{i}_m\}}$ . Note that this implies  $i_{dc} = \hat{i}_m$  during buck mode and  $i_{dc} = \hat{i}_g$  during boost mode. This corresponds to  $i_{dc,2}$  in **Fig. 3**, whose magnitude is clearly lower than  $i_{dc,1}$  for all part load operating points, hence resulting in lower losses. This mode of operation is hereafter referred to as the conventional operation for ac-ac CSC in this paper.

3) Variable dc-link current / synergetic control: However, there are still time intervals within each mains/motor period where  $i_{dc,2}$  is higher than the instantaneous maximum absolute value of the six phase currents (three on the grid side, three on the motor side). As proposed in [46] for an ac-dc rectifier and in [47] for a dc-ac CSI, shaping  $i_{dc}$  to the six-pulse (in a threephase system) envelope of the maximum absolute values of the phase currents not only leads to a further reduction of the conduction losses, but advantageously significantly reduces the transistor switching losses by avoiding high-frequency switching in some part of the fundamental ac period, i.e., realizes 2/3-PWM, which is further discussed in **Section II** below. The concept has further been discussed for dc-ac inverter applications [48], [49] and ac-dc rectifier applications [29], where in both cases additional dc-dc converter stages shape  $i_{dc}$ to the required six-pulse shape.

The applicability of this concept was extended to ac-ac CSCs by the authors in [40]. There, the CSI defines the dclink current reference in the buck mode and the CSR does so in boost mode, see  $i_{\rm dc,3}$  in **Fig. 3**; in the transition region, both stages define sections of the dc-link current reference alternately. Advantageously, the respective other converter stage

can shape the dc-link current accordingly; the CSR and the CSI thus *synergetically* control the dc-link current to the minimum possible value at all times and, in doing so, realize the minimum possible conduction losses and significant switching loss savings for the stage operating with 2/3-PWM (further explanation in **Section II**).<sup>3</sup>

Whereas [40] introduces synergetic control of ac-ac CSCs, only simulation results are presented, and the paper puts a focus on detailed characterization results of the novel 600 V,  $140\,\mathrm{m}\Omega$  GaN M-BDS in a CSC commutation cell. A detailed discussion and derivation of the synergetic control concept as well as an experimental validation are missing. Therefore, this paper first provides an in-depth explanation of the loss-optimal operating modes of an ac-ac CSC in terms of space vector modulation in Section II, which further provides closed-form solutions for the semiconductor losses and briefly mentions the impact of synergetic control on the design of the dclink inductor  $L_{dc}$ . Section III then presents the synergetic control structure that realizes loss-optimal operation of the ac-ac CSC throughout the operating area, ensuring seamless transitions between buck and boost operation. Section IV employs a full ac-ac CSC demonstrator with first-generation  $140 \,\mathrm{m}\Omega$ ,  $600 \,\mathrm{V}$  GaN M-BDSs to comprehensively validate the proposed synergetic control method in static and transient cases and to characterize the system-level efficiency improvements over the full output voltage/current range. Finally, Section V provides concluding remarks. In addition, Appendix A presents a concise overview of the basic operating principles of the current-source converters.

#### II. LOSS-OPTIMAL OPERATION OF AC-AC CSCs

For understanding the modulation of CSCs, it is helpful to consider the (quasi) duality relationship [50] to VSCs: Whereas in ac-ac VSCs a (constant) dc-link voltage is pulse-widthmodulated to synthesize the desired three-phase input/output low-frequency (LF) ac voltage waveforms, in ac-ac CSCs highfrequency (HF) switching is used to modulate a (typically constant) dc-link current, idc, into the desired three-phase input/output LF ac currents. Therefore, each CSC switching stage (CSR and CSI) comprises two commutation cells (see Fig. 1). Interfacing a three-phase ac system, each commutation cell comprises three BDSs, and each BDS connects the dclink inductor to one of the three ac-side phase terminals. Further, there are three ac-side commutation capacitors in each commutation cell, which can be arranged in star or delta configuration; note that the dc-link inductor terminal is the commutation cell's switching node. Therefore, at least one (to ensure a path for the inductive  $i_{dc}$ ) and only one (to avoid short-circuiting the ac-side commutation and filter capacitors) BDS in each commutation cell must be turned-on at all times.

<sup>3</sup>It should be noted that of the three options for selecting  $i_{\rm dc}$ , non-adaptive constant dc-link current ( $i_{\rm dc}=i_{\rm dc,1}$  in **Fig. 3**) offers the highest system dynamics since a step increase of the output current reference only requires a change in  $m_{\rm i}$  whereas for the other two options ( $i_{\rm dc}=i_{\rm dc,2}$  or  $i_{\rm dc,3}$  in **Fig. 3**), first the dc-link current must be increased with finite dynamics of the dc-link current control loop. However, a large share of applications (like fans or pumps) do not require high control dynamics and hence can benefit from the efficiency improvement achievable by adapting the dc-link current to the

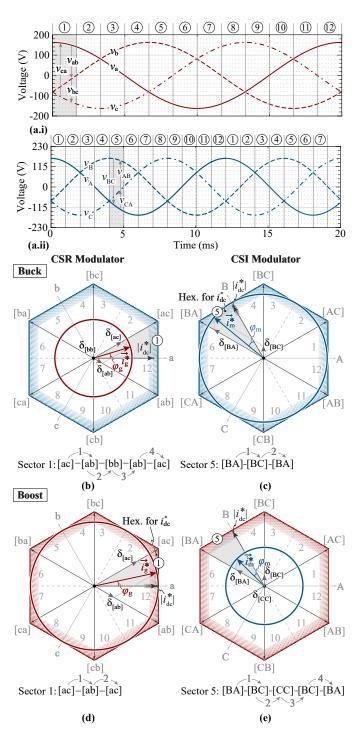

**Fig. 4.** Space-vector (SV) modulation of CSCs. (a.i) Three-phase grid voltage and (a.ii) three-phase motor voltage system with fundamental frequency of 50Hz and 80Hz divided into 12 sectors. SV diagrams for (b), (d) the CSR and (c), (e) the CSI of the ac-ac CSC, with exemplary CSR current reference SV  $\vec{i}_{\rm m}^*$  in sector 1 and exemplary CSI current reference SV  $\vec{i}_{\rm m}^*$  in sector 5, respectively, for buck ((b), (c)) and boost ((d), (e)) operation. For the proposed loss-optimal synergetic operation, the dc-link current  $\vec{i}_{\rm dc}^*$  varies according to (8)), which implies a continuous scaling of the hexagon size as indicated by the shaded areas. In buck operation, the CSI currents  $\vec{i}_{\rm A,s}^*$ ,  $\vec{i}_{\rm B,s}^*$  and  $\vec{i}_{\rm C,s}^*$  define  $\vec{i}_{\rm dc}$ ;  $\vec{i}_{\rm m}^*$  is thus advantageously synthesized without a zero vector and with only two switching transitions in each switching period (see (c)). In contrast, the SV sequence required to synthesize  $\vec{i}_{\rm g}^*$  involves a zero vector ([bb] for sector 1) and a total of four switching transition (see (b)). These roles of the CSR and the CSI swap during boost operation (see (d) and (e)).

The switching states of a CSR or CSI are thus represented as [xy] where 'x' and 'y' denote the phases that connect to the dc-link in the high-side commutation cell (e.g.,  $CS_h$  in **Fig. 1**) and in the low-side commutation cell, respectively. Each switching state corresponds to a *current* space vector (SV, representing the instantaneous phase currents) generated on the ac side: For a three phase system there are six active vectors with  $x \neq y$  and length  $2/\sqrt{3} \cdot i_{dc}$  (see **Fig. 4**), which implies energy transfer between the dc-link and the ac side. There are further three zero vectors (free-wheeling states<sup>4</sup>) where x = y, which corresponds to free-wheeling of  $i_{dc}$  from the high-side to the low-side commutation cell with (instantaneously) zero current routed to any of the three phases.

To synthesize a desired local average (over one switching period) ac-side current SV, e.g.,  $\vec{i}_g^*$  in **Fig. 4b**, the two adjacent active SVs and any of the three zero SVs are applied during respective dwell times, such that in average  $\vec{i}_g^*$  results. Not that if only active vectors were used, the correct direction (angle) of  $\vec{i}_g^*$  could be achieved, but the length would depend on  $i_{dc}$ ; a zero vector is thus needed to scale the length of the synthesized SV accordingly.

It is thus useful to divide the corresponding current SV diagram into twelve sectors based on the active vectors and on the sequence of active and zero vectors used for synthesizing a desired ac-side current SV [15]. For instance, the grid current reference  $i_g^*$  in **Fig. 4b** is in sector 1 and thus synthesized using the two adjacent active vectors [ac] and [ab]; the choice of zero vector, however, presents a degree of freedom for modifying various performance indicators like overall switching losses, generated common-mode (CM) voltage, dc-link current ripple, etc.: In CSCs, a switching transition involves a fixed current  $i_{\rm dc}$  and a time-varying line-to-line voltage. Again considering the exemplary sector 1 from Fig. 4b and assuming unity power factor operation, the line-to-line voltages are  $|v_{bc}| < |v_{ab}| <$  $|v_{\rm ca}|$  (see **Fig. 4a**). Therefore, to avoid switching the line-toline voltage with the highest magnitude,  $v_{ca}$ , the zero vector [cc] is not used in sector 1. The two remaining zero vectors [aa] (switching sequence: [ac]-[ab]-[aa]-[ab]-[ac]) and [bb] (switching sequence: [ac]-[ab]-[bb]-[ac]) result in lower but identical switching losses, since both sequences lead to two hard and two soft commutations with the line-to-line voltage magnitudes  $|v_{bc}|$  and  $|v_{ab}|$ .

For unity power factor, using the zero vector [aa] keeps phase a clamped to the positive dc-link current (i.e., the high-side commutation cell is not switching), but leads to the highest magnitude of the generated CM voltage, with the CM voltage of the CSR defined as  $v_{\rm CM} = (v_{\rm pk} + v_{\rm nk})/2$  (cf. **Fig. 2** and **Fig. 5** in [52]). Extending this criterion for the selection of the zero vector to the other sectors further leads to discontinuities in the local-average CM voltage at every second sector boundary. Instead, using [bb] (in the exemplary sector 1) results in the lowest CM voltage since  $|v_{\rm a}| > |v_{\rm b}|$  are the phase voltages with the highest and the lowest magnitude in sector 1, respectively. Further, using the zero vector corresponding to the phase with the respective lowest instantaneous voltage value ([bb] in

<sup>4</sup>The free-wheeling states are alternatively named as "shoot-through" states [51].

the exemplary sector 1) results in a continuous local average CM voltage [52], [53] and further results in a more uniform distribution of the instantaneous conduction and switching losses among the BDSs, which is particularly important for operation with very low ac fundamental frequencies (low motor speed) [54]. Therefore, we consider this variant (phase with lowest voltage magnitude defining the zero vector, i.e., switching sequence [ac]-[ab]-[bb]-[ab]-[ac] in the exemplary sector 1) for the further analysis.

For an ac-ac CSC with its back-to-back connected CSR and CSI, there are two independently working SV modulators responsible for synthesizing the CSR current vector  $\vec{i}_g^* = \hat{l}_g^* \cdot e^{j\omega_g t}$  and the CSI current vector  $\vec{i}_m^* = \hat{l}_m^* \cdot e^{j\omega_m t}$ , respectively, using the common  $i_{dc}$  (see **Fig. 4**). The dwell times of the active and zero vectors of the CSR are

$$\begin{split} \delta_{[g+]} &= m_{\rm g} \cdot \cos(\varphi_{\rm g} - \pi/3) \\ \delta_{[g-]} &= m_{\rm g} \cdot \cos(\varphi_{\rm g} + \pi/3) \\ \delta_{[g0]} &= 1 - \delta_{[g+]} - \delta_{[g-]}, \end{split} \tag{2}$$

where  $\delta_{[g+]}$  and  $\delta_{[g-]}$  are the dwell times of the active vectors immediately leading and lagging  $\vec{i}_g^*$  in counter-clockwise direction, and  $\delta_{[g0]}$  is the dwell time of the zero vector. For example, considering  $\vec{i}_g^*$  in sector 1 as shown in **Fig. 4b**, we have  $\delta_{[g+]} = \delta_{ac}$ ,  $\delta_{[g-]} = \delta_{ab}$  and  $\delta_{[g0]} = \delta_{bb}$ . Further,  $\varphi_g$  is the within-sector angle defined as

$$\varphi_{\rm g} = \omega_{\rm g} t - \lfloor \frac{{\rm sect}_{\rm CSR}}{2} \rfloor \cdot \frac{\pi}{3},$$

(3)

where  $\text{sect}_{\text{CSR}}$  denotes the sector (see **Fig. 4**) of  $\vec{i}_g^*$ ,  $\lfloor x \rfloor$  denotes the floor function and hence  $\varphi_g \in [-\pi/6, \pi/6]$ . Similarly, the dwell times of the CSI are

$$\delta_{[m+]} = m_{m} \cdot \cos(\varphi_{m} - \pi/3)$$

$$\delta_{[m-]} = m_{m} \cdot \cos(\varphi_{m} + \pi/3)$$

$$\delta_{[m0]} = 1 - \delta_{[m+]} - \delta_{[m-]},$$

(4)

where  $\delta_{[\mathrm{m}+]}$  and  $\delta_{[\mathrm{m}-]}$  are the dwell times of the active vectors immediately leading and lagging  $\vec{i}_{\mathrm{m}}^*$  in counter-clockwise direction, and  $\delta_{[\mathrm{m}0]}$  is the dwell time of the zero vector. For example, for  $\vec{i}_{\mathrm{m}}^*$  in sector 5 as shown in **Fig. 4e**, we have  $\delta_{[\mathrm{m}+]} = \delta_{\mathrm{BA}}$ ,  $\delta_{[\mathrm{m}-]} = \delta_{\mathrm{BC}}$  and  $\delta_{[\mathrm{m}0]} = \delta_{\mathrm{CC}}$ . Finally, the withinsector angle is

$$\varphi_{\rm m} = \omega_{\rm m} t - \lfloor \frac{{\rm sect}_{\rm CSI}}{2} \rfloor \cdot \frac{\pi}{3},$$

with  $sect_{CSI}$  denoting the sector of  $\vec{i}_{m}^{*}$ .

A. Conventional Operation - Adaptive Constant DC-Link Current

As discussed above in **Section I**, the ac-ac CSC's CSR conventionally regulates  $i_{\rm dc}$  to a constant value while the CSI uses this dc-link current to synthesize the desired motor currents. The reference value for  $i_{\rm dc}$  is thus calculated as

$$i_{\text{dc.conv}}^* = \max\left(\hat{i}_g^*, \hat{i}_m^*\right),\tag{5}$$

corresponding to  $i_{dc,2}$  in **Fig. 3** in the case of adaptive constant dc-link current. Therefore, during buck operation  $i_{dc,conv}^* = \hat{i}_{m}^*$

as shown in **Fig. 5a** (left part) with simulated key waveform of the considered ac-ac CSC from **Fig. 1** with specifications given in **Tab. I**. This implies that the CSR and CSI modulation indices are:

$$m_{\mathrm{g,conv}} \left( = \frac{\hat{i}_{\mathrm{g}}^*}{i_{\mathrm{dc,conv}}^*} \right) < 1, \quad m_{\mathrm{m,conv}} \left( = \frac{\hat{i}_{\mathrm{m}}^*}{i_{\mathrm{dc,conv}}^*} \right) = 1.$$

Similarly, for boost operation,  $i_{dc,conv}^* = \hat{i}_g^*$  (see **Fig. 5a**, right part) implies  $m_{g,conv} = 1$  and  $m_{m,conv} < 1$ .

From (2) and (4), clearly  $m_{\rm g,conv}$  < 1 results in  $\left(\delta_{[g+]} + \delta_{[g-]}\right) < 1$  and hence  $\delta_{[g0]} > 0$  at all times during buck operation, i.e., the CSR modulation must use zero vectors. Similarly,  $m_{\rm m,conv} < 1$  leads to  $(\delta_{\rm [m+]} + \delta_{\rm [m-]}) < 1$  and hence  $\delta_{\rm m0} > 0$  at all times during boost operation, i.e., the CSI modulation must use zero vectors. However, even the stage that defines  $i_{dc,conv}^*$  according to (5) and hence operates with unity modulation index requires zero vectors, since  $m_{\rm m,conv} = 1$ during buck operation also leads to  $(\delta_{[m+]} + \delta_{[m-]}) < 1$  if  $\varphi_{\rm m} \neq 0$ , and  $m_{\rm g,conv} = 1$  during boost operation results in  $(\delta_{g+1} + \delta_{g-1})$  < 1 if  $\varphi_g \neq 0$ . The presence of a zero vector in the switching sequence results in a total of four switching transitions per switching period (two hard and two soft transitions; for example in **Fig. 4b**, the sequence [ac]-[ab]-[bb]-[ab]-[ac] leads to switching of  $v_{\rm cb}, v_{\rm ab}, v_{\rm ba}$  and  $v_{\rm bc})$  and includes high-frequency modulation of  $i_{dc}$  to synthesize all three phase currents during a switching period (3/3-PWM).

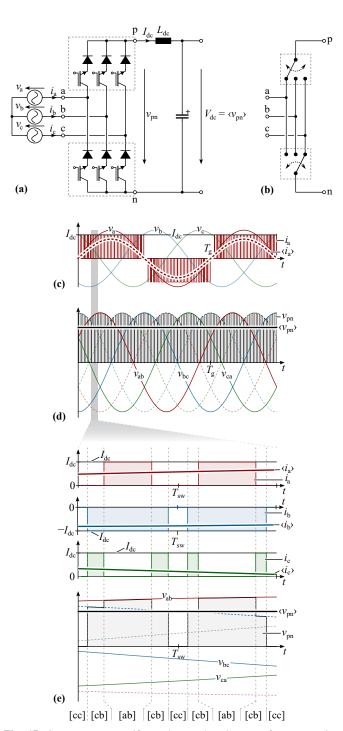

Conventionally, thus, both, the CSR and the CSI, operate with 3/3-PWM irrespective of the operating point, as shown in **Fig. 5a**: The 3/3-PWM of the CSR and and the CSI is evident from the respective switched dc-side voltages  $v_{\rm pn}$  and  $v_{\rm PN}$ , which toggle between zero (zero vector) and the line-to-line voltages (active vectors) which correspond to the respective switching states, as well as from the switched currents  $i_{\rm a,s}$  and  $i_{\rm A,s}$ , respectively (see **Fig. 1**), which toggle between zero (zero vector) and  $\pm i_{\rm dc,conv}$  (active vector).

#### B. Proposed Loss-Optimal Operation

Again, as briefly introduced in **Section I**, selecting a time-varying dc-link current  $i_{\rm dc}$  of a CSR or a CSI equal to the instantaneous maximum absolute value of the three ac phase current references eliminates the need for using zero vectors [29], [46]–[49]. The corresponding dc-link current references for the CSC's CSR and CSI, respectively, are

$$i_{\text{dc,CSR}}^*(t) = \max \left\{ |i_{\text{a,s}}^*(t)|, |i_{\text{b,s}}^*(t)|, |i_{\text{c,s}}^*(t)| \right\}$$

and (6)

$$i_{\text{dc CSI}}^*(t) = \max\left\{ |i_{\text{A s}}^*(t)|, |i_{\text{B s}}^*(t)|, |i_{\text{C s}}^*(t)| \right\}. \tag{7}$$

Considering, for example, the CSI, the dc-link current thus equals (the absolute value of) one of the three phase currents during an entire sector. Therefore, the corresponding phase terminal is continuously connected to either the positive or the negative dc-link terminal, while only the two other phase currents must be synthesized with PWM (2/3-PWM). In the exemplary case shown in **Fig. 4c**, the switching sequence [BA]-[BC]-[BA] indicates that phase B is clamped to the positive dc-link terminal by the high-side commutation cell, while the low-side commutation cell operates two out of its three transistors with PWM, distributing the dc-link current between

phases A and C. The corresponding absence of a zero vector advantageously reduces the number of switching transitions per switching period from four (3/3-PWM, see above) to two (one hard and one soft transition involving  $v_{AC}$  and  $v_{CA}$ ).

The elimination of zero vectors with (6) and (7) can be easily verified with dwell time calculations according to (2) and (4), respectively. Maintaining  $i_{\text{dc,CSR}}^*(t)$  according to (6) implies  $i_{\text{dc,CSR}}^*(t) = \hat{i}_g^*\cos(\varphi_g) \implies m_g(t) = 1/\cos(\varphi_g)$  which leads to  $\delta_{[g+]} + \delta_{[g-]} = 1 \implies \delta_{[g0]} = 0 \ \forall \varphi_g$  [49]. Similarly, maintaining  $i_{\text{DC,CSI}}^*(t)$  according to (7) leads to  $m_{\text{m}}(t) = 1/\cos(\varphi_{\text{m}}) \implies \hat{\delta}_{[\text{m+}]} + \delta_{[\text{m-}]} = 1 \implies \delta_{[\text{m0}]} = 0 \ \forall \varphi_{\text{m}}$ .

In an ac-ac CSC, the CSR and the CSI share the same dc-link current, which hence must be selected according to

$$i_{dc,syn}^{*}(t) = \max \left\{ i_{dc,CSR}^{*}(t), i_{dc,CSI}^{*}(t) \right\}.$$

(8)

Doing so ensures that at any point in time, either the CSR or the CSI operates with 2/3-PWM, while the other stage must operate with 3/3-PWM and shape the dc-link current accordingly, i.e., the two stages operate in a synergetic manner to minimize the overall losses. This is visualized in **Fig. 3** and in the SV diagrams of **Fig. 4b,c** for buck operation where the CSI defines  $i_{\text{dc,syn}}^*(t)$  according to (7) and operates with 2/3-PWM. The dc-link current  $i_{\text{dc,syn}}^*(t)$  thus varies according to  $\hat{i}_{\text{m}}^* \cos(\varphi_{\text{m}})$  with  $\varphi_{\text{m}} \in [-\pi/6, \pi/6]$ , which corresponds to a scaling of the SV hexagon such that  $i_{\text{m}}^*$  always coincides with its perimeter. In buck mode, the magnitude of  $i_{\text{g}}^*$  is smaller than that of  $i_{\text{m}}^*$ , i.e., the circular trajectory of  $i_{\text{g}}^*$  lies always within the hexagon, which implies 3/3-PWM for the CSR.

**Fig. 5b** shows simulated key waveforms, where buck operation occurs for  $V_{\rm m}/V_{\rm g} < \sqrt{3}/2$ . Then, the dc-link current's six-pulse shape is defined by the motor currents according to (7). The absence of free-wheeling states (zero vectors) during 2/3-PWM operation of the CSI is visible in the waveform of  $v_{\rm PN}$ , which never reaches zero and only switches between two of the three line-to-line voltage absolute values ( $|v_{\rm XY}|$  and  $|v_{\rm XZ}|$ , where X refers to the clamped phase with the highest absolute value of current). Further, note that the CSI's output current, e.g.,  $i_{\rm A,s}$ , shows intervals without PWM operation when  $i_{\rm dc,CSI}^*(t) = |i_{\rm A}(t)|$  and hence  $|i_{\rm A,s}| = i_{\rm dc,syn}$ , which allows clamping of phase A to the dc-link. On the other hand, 3/3-PWM operation of CSR results in switching of  $v_{\rm pn}$  between zero and two other line-to-line voltages, and  $i_{\rm a,s}$  is always switching between zero and  $i_{\rm dc,syn}$ .

**Fig. 4d,e** depict the SV diagrams for boost operation, where the roles of the CSR and the CSI are swapped, i.e., the CSR now defines  $i_{dc,syn}^*(t)$  according to (6) and operates with 2/3-PWM while the CSI operates with 3/3-PWM. Similarly, **Fig. 5b** shows boost operation for  $V_m/V_g > 2/\sqrt{3}$ , where now  $v_{pn}$  never attains zero and the switched current of the CSR's phase a shows clamping intervals with  $i_{a,s} = i_{dc,syn}$  when  $i_{dc,CSR}^*(t) = |i_a(t)|$ , i.e., the CSR operates with 2/3-PWM. On the other hand,  $v_{PN}$  switches between zero and line-to-line voltages and  $i_{A,s}$  always toggles between zero and  $i_{dc,syn}$ , i.e., the CSI operates with 3/3-PWM. Note the change in frequency of  $i_{dc,syn}$  in boost compared to buck operation, which is a consequence of the generally different grid and motor frequencies.

Fig. 5. Simulated key waveforms of the ac-ac CSC from Fig. 1 with  $V_{\rm g,n}=200\,{\rm V}$ ,  $f_{\rm g}=50\,{\rm Hz}$ ,  $f_{\rm m}=100\,{\rm Hz}$  and  $V_{\rm m}$  increasing from  $100\,{\rm V}$  to  $283\,{\rm V}$  with a maximum power limit of  $P_{\rm n}=1.4\,{\rm kW}$  according to Fig. 2. (a) Conventional and (b) proposed synergetic control: for  $V_{\rm m}/V_{\rm g}<\sqrt{3}/2$  (buck), the CSR operates with 3/3-PWM and regulates  $i_{\rm dc}$  such that the CSI operates with 2/3-PWM. Similarly, for  $V_{\rm m}/V_{\rm g} > 2/\sqrt{3}$  (boost), the CSR operates with 2/3-PWM and defines the reference for  $i_{\rm dc}$ , which is regulated by the CSI thus operating with 3/3-PWM. For  $\sqrt{3}/2 < V_{\rm m}/V_{\rm g} < 2/\sqrt{3}$  (transition mode), both, the CSR and the CSI alternatingly operate with 2/3-PWM and 3/3-PWM. Conduction and switching losses are calculated considering measurements [40] of first-generation 600 V, 140 m $\Omega$  GaN M-BDSs. Note that in a motor application, an increase of the motor/output voltage is coupled to an increase of the output frequency; this increase in frequency is, however, not important for the explanation of the proposed synergetic control method and therefore not shown for the sake of better visibility.

Note that the local average values of  $v_{PN}$  and  $v_{pn}$  follow the six pulse shape of  $i_{dc,syn}$  but in opposite relation, i.e.,  $v_{PN,avg}$  and  $v_{pn,avg}$  are at their maxima when  $i_{dc,syn}$  is at it's minimum and vice versa, as expected from the constant power flow through the dc-side interfaces of the CSR and the CSI.

Finally, for  $\sqrt{3}/2 < V_{\rm m}/V_{\rm g} < 2/\sqrt{3}$ , i.e., in the transition region between buck and boost operation, the CSR and the CSI interchangeably operate with 2/3-PWM and 3/3-PWM depending on the instantaneous value of max  $\{i_{\rm dc,CSR}^*(t),i_{\rm dc,CSI}^*(t)\}$ , which is visible in the waveforms of  $v_{\rm pn}$  and  $v_{\rm PN}$ , respectively.

It is therefore possible to always operate one of the ac-ac CSC's two stages with 2/3-PWM and hence with minimum possible dc-link current, which ensures minimum possible

switching and conduction losses as discussed in the following; then, **Section III** introduces a synergetic control method that ensures this loss-optimal mode of operation.

#### C. Losses in Conventional and Loss-Optimal Operation

The quantitative reduction in losses achieved through lossoptimal operation / synergetic control of the ac-ac CSC are discussed based on closed-form expressions for transistor conduction and switching losses.

1) Conduction Losses: Since, at any point in time, four (and only four) M-BDSs conduct the dc-link current, the conduction

losses with conventional (see **Subsection II-A** above) operation of the ac-ac CSC are

$$P_{\text{cond,conv}} = 4 \cdot i_{\text{dc,conv}}^2 \cdot R_{\text{ds,on}}, \tag{9}$$

where  $R_{ds,on}$  is the on-state resistance of an M-BDS and,  $i_{dc,conv}$  is calculated according to (5).

Instead, for loss-optimal operation, the dc-link current is shaped according to (8), i.e., always attains the minimum value necessary to synthesize the grid and motor currents (see **Fig. 5b**). This results in a lower rms value of

$$i_{\text{rms,syn}} = \sqrt{\frac{3}{\pi} \left[ \int_{-\pi/6}^{\pi/6} \max \left\{ \hat{i}_{\text{g}}, \hat{i}_{\text{m}} \right\}^{2} \cos^{2} \left( \varphi \right) d\varphi \right]}$$

$$\approx 0.956 \cdot i_{\text{dc conv}}.$$

Therefore, the total conduction losses are

$$P_{\text{cond,syn}} \approx 0.91 \cdot 4 \cdot i_{\text{dc,conv}}^2 \cdot R_{\text{ds,on}},$$

(10)

i.e., reduced by around 9% compared to conventional operation. Note that the lower rms value of the dc-link current not only benefits the transistors, but also reduces the winding losses of the dc-link inductor  $L_{\rm dc}$  accordingly.

Considering, first-generation 600 V,  $140\,\mathrm{m}\Omega$  M-BDSs [40], **Fig. 5** shows the instantaneous conduction losses  $p_{\mathrm{cond},S,\mathrm{ah}}$  of a CSR M-BDS  $S_{\mathrm{ah}}$  and  $p_{\mathrm{cond},S,\mathrm{Ah}}$  of a CSI M-BDS  $S_{\mathrm{Ah}}$  (see **Fig. 1**) for both, conventional and loss-optimal operation and a varying input/output voltage ratio,  $V_{\mathrm{m}}/V_{\mathrm{g}}$ . Considering the operation with adaptive constant dc-link current (see **Fig. 5a**), the dc-link current does not change with the input/output voltage ratio and hence the average conduction losses of  $S_{\mathrm{ah}}$  and  $S_{\mathrm{Ah}}$  are independent of the input/output voltage ratio and further equal to each other. A like observation holds for loss-optimal operation (see **Fig. 5b**), where the average conduction losses are reduced to about 91%.

Note, however, that the evolution of  $p_{cond,S,ah}$  within a fundamental period shows a more even distribution with lower peak value in buck operation compared to boost operation (the opposite behavior is observed for  $p_{cond,S,Ah}$ ). This is a consequence of the active/zero vector selection and the respective dwell times, e.g., in buck mode, in any switching period,  $S_{ah}$  is either used by the active vectors or by the zero vector, but not by both, which lowers the peak conduction losses for the short dwell times of the active vectors in buck mode (low grid current compared to the dc-link current).

2) Switching Losses: Conventionally, both stages of the the ac-ac CSC operate with 3/3-PWM. Considering, as an example, sector 1 of the CSR during buck operation (see **Fig. 4b**), there are four transitions per switching period, with switched voltages of  $v_{\rm cb}$ ,  $v_{\rm ab}$ ,  $v_{\rm ba}$  and  $v_{\rm bc}$ . Since the direction of the dc-link current  $i_{\rm dc}$  is fixed, two of these transitions are hard-switching transitions ( $v_{\rm ba}$  and  $v_{\rm bc}$ ) and two are soft-switching transitions ( $v_{\rm cb}$  and  $v_{\rm ab}$ ), i.e., the overall switching losses are equivalent to those of two half bridges operating with the voltages  $v_{\rm bc}$  and  $v_{\rm ab}$ , and the current  $i_{\rm dc}$ . Owing to the symmetry between sectors, the overall switching losses of

the CSR-stage operating with 3/3-PWM and unity power factor are thus

$$P_{\text{sw,csr,conv}} = f_{\text{sw}} \cdot \frac{6}{\pi} \left[ \int_0^{\pi/6} \left( e_{\text{sw}} \left( i_{\text{dc,conv}}, v_{\text{ab}} \right) + e_{\text{sw}} \left( i_{\text{dc,conv}}, v_{\text{bc}} \right) \right) d\varphi_{\text{g}} \right],$$

(11)

with  $f_{sw}$  denoting the switching frequency and where

$$e_{sw}(i_{sw}, v_{sw}) = k_1 \cdot i_{sw} \cdot v_{sw} + k_2 \cdot v_{sw}^2$$

(12)

is the total half-bridge switching energy (i.e., sum of the turn-on and the turn-off energy), with  $i_{sw}$  and  $v_{sw}$  denoting the switched current and voltage, respectively. For the considered 600 V, 140 m $\Omega$  GaN M-BDS, the authors have presented corresponding calorimetric measurements<sup>5</sup> in [40], resulting in  $k_1 = 2.16 \times 10^{-8} \, \mathrm{J/(VA)}$  and  $k_2 = 1.3 \times 10^{-10} \, \mathrm{J/V^2}$ .

Evaluating the integral from (11) then yields a closed-form expression for the CSR-stage switching losses:

$$P_{\text{sw,csr,conv}} = \frac{3\hat{V}_{g}f_{\text{sw}}}{\pi} \left[ k_{1}i_{\text{dc,conv}} + k_{2}\hat{V}_{g} \frac{4\pi - 3\sqrt{3}}{12} \right].$$

(13)

Similarly, the switching losses of the CSI with conventional operation (3/3-PWM) under unity power factor are

$$P_{\text{sw,csi,conv}} = \frac{3\hat{V}_{\text{m}}f_{\text{sw}}}{\pi} \left[ k_1 i_{\text{dc,conv}} + k_2 \hat{V}_{\text{m}} \frac{4\pi - 3\sqrt{3}}{12} \right]. \tag{14}$$

Instead, with loss-optimal operation of the ac-ac CSC, the stage operating with 2/3-PWM has only two (instead of four) switching transitions per switching period. Considering, for instance, sector 5 of the CSI during buck operation (see **Fig. 4b**), the switched voltages are  $V_{\rm AC}$  and  $V_{\rm CA}$ . Again, since the direction of the dc-link current  $i_{\rm dc}$  is fixed, there is only one hard and one soft transition. Following the derivation of (13), the overall switching losses of the stage operating with 2/3-PWM are

$$P_{\text{sw,23,syn}} = \frac{3\hat{V}_{23}f_{\text{sw}}}{\pi} \left[ \frac{k_1\hat{i}_{\text{dc,syn}}}{4} + k_2\hat{V}_{23}\frac{2\pi - 3\sqrt{3}}{12} \right], \quad (15)$$

where  $\hat{i}_{\text{dc,syn}}$  is the peak value of the loss-optimum dc-link current from (8), i.e.,  $\hat{i}_{\text{dc,syn}} = \max \left\{ \hat{i}_{\text{g}}, \hat{i}_{\text{m}} \right\} = i_{\text{dc,conv}}$ . Further,  $\hat{V}_{23}$  is the peak line-to-line voltage of the stage operated with 2/3-PWM. For the same system parameters, operating the CSR or the CSI with 2/3-PWM instead of with 3/3-PWM thus reduces the switching losses of that stage by around 76% at the nominal operating point<sup>6</sup>.

$^5 \rm Since~a~CSC$  commutation cell has three switches connected to a common switched node, the switching transition between any two of these switches forces a change of voltage across the third switch as well, which incurs additional  $C_{\rm oss}$  losses. However, as confirmed by measurements in [40], the overall contribution over a mains period is small enough to be neglected.

<sup>6</sup>The reduction in switching losses with 2/3-PWM is calculated for the case where the zero vectors for 3/3-PWM are selected to minimize the amplitude of the switched voltage as discussed at the beginning of **Section II**. Choosing the zero vector differently can potentially result in even higher savings of switching losses. Further note that the reduction of switching losses depend on the ratio of  $k_1/k_2$ . Therefore, employing transistors with different switching loss characteristics will result in different savings of switching losses.

For loss-optimal operation of the ac-ac CSC, one of the stages still operates with 3/3-PWM (CSR during buck and CSI during boost operation) but, in contrast to the conventional case, with lower and time-varying dc-link current  $i_{\rm dc,syn}$ , whereby the shape of  $i_{\rm dc,syn}$  depends on the fundamental frequency of the other stage operating with 2/3-PWM. This implies that the switching losses of the stage operated with 3/3-PWM are a function of both,  $\varphi_{\rm g}$  and  $\varphi_{\rm m}$ , which complicates the derivation of a closed-form solution. It has, however, been verified by simulation that the difference in switching losses of the stage operating with 3/3-PWM when the fundamental frequency of the other stage operating with 2/3-PWM is varied between 1 Hz and 200 Hz is negligible. Therefore, assuming the same fundamental frequency on the grid and motor side, the switching losses of the stage operating with 3/3-PWM are

$$P_{\text{sw,33,syn}} = \frac{3\hat{V}_{33}f_{\text{sw}}}{\pi} \left[ k_1 \hat{i}_{\text{dc,syn}} \frac{\sqrt{3}\pi + 6}{12} + k_2 \hat{V}_{33} \frac{4\pi - 3\sqrt{3}}{12} \right],$$

where  $\hat{V}_{33}$  is the peak line-to-line voltage of the stage operating with 3/3-PWM. For operating the CSR or the CSI with 3/3-PWM according to loss optimal operation, that is, with the other stage operated with 2/3-PWM, the switching losses of that stage are reduced by around 4% at nominal operating point compared to conventional operation.

The total switching losses for conventional and loss-optimal operation of the ac-ac CSC are therefore

$$P_{\text{sw,conv}} = P_{\text{sw,csr,conv}} + P_{\text{sw,csi,conv}}$$

and (17)

$$P_{\text{sw,syn}} = P_{\text{sw,23,syn}} + P_{\text{sw,33,syn}},$$

(18)

respectively, whereby the roles (2/3-PWM, 3/3-PWM) of the CSR and the CSI change depending on the ratio of input to output voltage.

**Fig. 5** shows the instantaneous switching losses  $p_{\rm sw,S,ah}$  of the CSR's M-BDS  $S_{\rm ah}$  and  $p_{\rm sw,S,Ah}$  of the CSI's M-BDS  $S_{\rm Ah}$  (see **Fig. 1**) for conventional and loss-optimal operation. For conventional operation, the CSR's switching losses do not depend on the output voltage (buck or boost mode) as a result of the fixed grid voltage and constant magnitude of  $i_{\rm dc,conv}$  during the simulation, see **Fig. 5a**. In contrast, loss-optimal operation implies 2/3-PWM operation of the CSR during boost

mode and thus considerably lower switching losses; this is also visually evident in **Fig. 5b** from the superimposed total loss envelopes for conventional operation. Note that even in buck mode (when the CSR operates with 3/3-PWM), there is a slight reduction of losses as expected from (16), i.e., because loss-optimal operation implies that the minimum possible dc-link current is used.

The switching losses of the CSI increase during the transition from buck to boost mode with both, conventional and loss-optimal operation, because of the increasing motor-side ac voltage. For loss-optimal operation, the CSI operates with 2/3-PWM in buck mode, which again results in loss savings as shown in **Fig. 5b**; since the load voltage is then relatively low (buck mode), the reduction in switching losses is less pronounced than in case of the CSR operating with 2/3-PWM in boost mode.

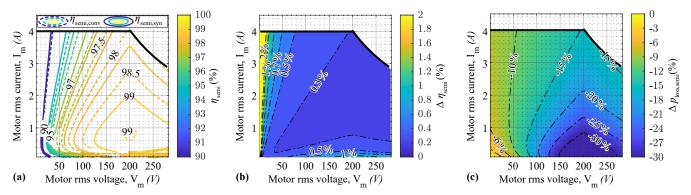

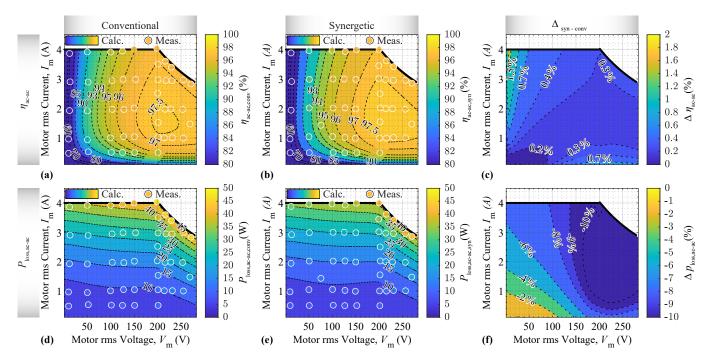

3) Comparison: Based on the closed-form expressions for semiconductor conduction and switching losses derived above, and considering first-generation  $600 \, \text{V}$ ,  $140 \, \text{m}\Omega$  GaN M-BDSs, **Fig. 6a** visualizes how loss-optimal/synergetic operation increases the semiconductor efficiency throughout the operating area. Similarly, **Fig. 6b** shows the percentage-point increase of the semiconductor efficiency and **Fig. 6c** shows the normalized semiconductor loss reduction. The semiconductor efficiency with loss-optimal/synergetic operation is necessarily higher than with conventional operation throughout the operating region, because always one stage operates with 2/3-PWM and the minimum possible dc-link current is used, irrespective of buck, boost, or transition region.

Note that the efficiency improvement depends on the selected device and switching frequencies; it will be higher for devices with larger chip area, i.e., designs using future M-BDSs with a lower on-state resistance and consequently higher output capacitance are expected to benefit more from loss-optimal/synergetic operation.

Further, note that the loss-optimal operation results in a slightly lower worst-case voltage-time area applied to the dc-link inductor. Therefore, and because of the lower dc-link current, in principle a minor reduction in size could be achieved if specifically designed for a CSC that always employs loss-optimal operation.

**Fig. 6.** Semiconductor loss reduction through loss-optimal operation of an ac-ac CSC using 600 V, 140 mΩ GaN M-BDSs and a switching frequency of  $f_{\rm sw} = 72$  kHz. (a) Contours of semiconductor efficiencies in the operating area (see **Fig. 2**) for conventional, i.e. with adaptive constant  $i_{\rm dc}$  ( $\eta_{\rm semi,conv}$ ) and loss-optimal/synergetic ( $\eta_{\rm semi,syn}$ ) operation. (b) Percentage-point change in semiconductor efficiency,  $\Delta \eta_{\rm semi} = \eta_{\rm semi,syn} - \eta_{\rm semi,conv}$ , and (c) relative reduction in semiconductor losses,  $\Delta p_{\rm loss,semi} = (p_{\rm loss,semi,syn} - p_{\rm loss,semi,conv}) \cdot 100/p_{\rm loss,semi,conv}$  achieved with loss-optimal/synergetic instead of conventional operation.

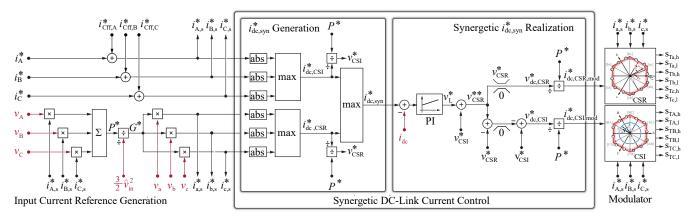

Fig. 7. Exemplary motor speed control loop that generates the motor current references,  $i_{\text{M}}^*$ , which are the inputs for the synergetic control structure from Fig. 8.

Fig. 8. Block diagram of the proposed synergetic control of the ac-ac CSC from Fig. 1, which ensures loss-optimal operation with minimum possible dc-link current and 2/3-PWM of either the CSR or the CSI. Based on instantaneous (local average) quantities, the control structure ensures seamless transitions between buck (motor voltages are lower than the grid voltages) and boost mode (the motor voltages are higher than the grid voltages) and facilitates operation in the transition region, where the system essentially changes between buck and boost mode sequentially over fundamental grid or motor period.

#### III. Synergetic Control Implementation

This section details the proposed synergetic control method [40] that ensures loss-optimal operation (minimum possible delink current and 2/3-PWM of the CSR or the CSI) as described above in **Section II** for any operating point (see **Fig. 2**). In a VSD, there is an outer motor speed control loop (see **Fig. 7**) that, by using, e.g., field-oriented control, ultimately generates the motor phase current references  $i_A^*$ ,  $i_B^*$ , and  $i_C^*$ . These motor phase current references are then further processed by the proposed synergetic control method according to the block diagram shown in **Fig. 8** and discussed in the following. Note that all quantities used in the following refer to local average (over one switching period) values.

#### A. Input Current Reference Generation

The synergetic control of the ac-ac CSC requires both, input and output reference currents to obtain the required time-varying dc-link current value  $i_{\text{dc,syn}}^*$  with (8). The output current references are typically provided by an application-specific outer control loop (see **Fig. 7**). The feed-forward of the output filter capacitor ( $C_{\text{DM1}}$  in **Fig. 1**) currents,  $i_{\text{Cff,X}}^*$ ,  $X \in [A, B, C]$  can be added to the output current references to calculate the CSI current reference values  $i_{A,S}^*$ ,  $i_{B,S}^*$  and  $i_{C,S}^*$ .

CSI current reference values  $i_{A,s}^*$ ,  $i_{B,s}^*$  and  $i_{C,s}^*$ . Aiming for unity power factor operation, the CSR current reference values  $i_{a,s}^*$ ,  $i_{b,s}^*$ , and  $i_{c,s}^*$  are then generated from the power balance between motor and grid side as

$$i_{x,s}^* = G^* \cdot v_x$$

with  $x \in [a, b, c]$  and  $G^* = \frac{P^*}{\frac{3}{2}\hat{v}_g^2}$ , (19)

where  $v_x, x \in [a, b, c]$  are the measured grid phase voltages and  $\hat{v}_g$  is their amplitude, and  $G^*$  is the reference conductance.

The power reference  $P^*$  is generated from the CSI current references and the measured output voltage according to  $P^* = \sum \{v_X \cdot i_{X s}^*\}, X \in [A, B, C].^{7,8}$

#### B. DC-link Current Reference Generation

The dc-link current reference  $i_{\rm dc}^*$  is then calculated according to (6), (7), and (8) such that  $i_{\rm dc}^*$  always equals the maximum absolute value of all six phase current references, which enables 2/3-PWM for the stage with the higher phase current references. A PI controller acts on the deviation of the measured dc-link current  $i_{\rm dc}$  and the reference value  $i_{\rm dc}^*$  to generate the dc-link inductor voltage reference,  $v_{\rm L}^*$ , required to track  $i_{\rm dc}^*$ .

Also, based on  $i_{dc,CSR}^*$  and  $i_{dc,CSI}^*$ , which are the dc-link current references that would result in 2/3-PWM of the CSR or the CSI, respectively, the corresponding dc-link voltage references

$$v_{\text{CSR}}^* = \frac{P^*}{i_{\text{dc CSR}}^*} \quad \text{and} \quad v_{\text{CSI}}^* = \frac{P^*}{i_{\text{dc CSI}}^*}$$

(20)

are calculated, i.e., the dc-link voltage references that correspond to 2/3-PWM operation of the respective stage.

#### C. Synergetic Shaping of DC-link Current

The dc-link inductor voltage  $v_L$  is the difference between the two dc-side voltages  $v_{pn}$  and  $v_{PN}$ . To generate a desired

<sup>8</sup>Note that for non-unity power factor loads, e.g., an induction machine, the calculation of the (active) power reference  $P^*$  should be performed in the dq coordinate frame. The rest of the proposed synergetic control structure, however, remains the same.

<sup>&</sup>lt;sup>7</sup>Note that the power reference can also be obtained by the motor speed and torque reference, in which case, a measurement of output voltage will not be strictly required.

reference inductor voltage  $v_{\rm L}^*$ , at least one of the two dc-side voltage references must be modified accordingly. As one of the stages should operate with 2/3-PWM, the other stage is utilized for realizing  $v_{\rm L}^*$  by accordingly adjusting its dc-side voltage reference. This is the core mechanism of the synergetic control method and the implementation is detailed in the following.

First,  $v_{\rm L}^*$  is added to  $v_{\rm CSI}^*$  to form a virtual dc-side voltage reference for the CSR,  $v_{\rm CSR}^{***} = v_{\rm CSI}^* + v_{\rm L}^*$ , which would be the dc-side voltage that the CSR must generate to enable 2/3-PWM of the CSI with  $v_{\rm L}^*$  applied across  $L_{\rm dc}$ . However, this is only feasible if  $i_{\rm dc,CSI}^* > i_{\rm dc,CSR}^*$  (or, equivalently,  $v_{\rm dc,CSI}^* < v_{\rm dc,CSR}^*$ ), i.e., during buck operation. Assuming that  $v_{\rm L}^*$  is small, this condition corresponds to  $v_{\rm CSR}^{***} < v_{\rm CSR}^*$ , i.e., the limiter in the upper signal path is not active and the dc-link current reference fed to the CSR modulator is

$$i_{\rm dc,CSR,mod}^* = \frac{P^*}{v_{\rm dc,CSR}^*} = \frac{P^*}{v_{\rm L}^* + v_{\rm CSI}^*} > i_{\rm dc,CSR}^*. \label{eq:idc,CSR}$$

Hence the CSR operates with 3/3-PWM and controls the dc-link current. In the lower signal path,  $v_{\text{CSR}}^{**} - v_{\text{CSR}}^{*} < 0$  is clamped at zero and hence the dc-link current reference fed to the CSI modulator is

$$i_{\text{dc,CSI,mod}}^* = \frac{P^*}{v_{\text{dc,CSI}}^*} = \frac{P^*}{v_{\text{CSI}}^*} = i_{\text{dc,CSI}}^*,$$

which ensures 2/3-PWM operation of the CSI during buck operation. The modulator calculates the duty cycles for the transistors as discussed in **Section II**, i.e., in case a suitable dc-link current reference is used, no zero vectors are employed.

If, in contrast,  $v_{\rm CSR}^{**} > v_{\rm CSR}^{*}$  (and hence  $i_{\rm dc,CSI}^{*} < i_{\rm dc,CSR}^{*}$ , i.e., boost mode), the limiter in the upper signal path clamps at  $v_{\rm CSR}^{*}$  and the dc-link current reference fed to the CSR modulator becomes

$$i_{\mathrm{dc,CSR,mod}}^* = \frac{P^*}{v_{\mathrm{dc,CSR}}^*} = \frac{P^*}{v_{\mathrm{CSR}}^*} = i_{\mathrm{dc,CSR}}^*,$$

ensuring 2/3-PWM operation of the CSR in boost mode. In the lower signal path,  $\nu_{\text{CSR}}^{**}-\nu_{\text{CSR}}^{*}>0$  is not clamped and hence  $\nu_{\text{dc,CSI}}^{*}=\nu_{\text{CSI}}^{*}-(\nu_{\text{L}}^{*}+\nu_{\text{CSI}}^{*}-\nu_{\text{CSR}}^{*})=\nu_{\text{CSR}}^{*}-\nu_{\text{L}}^{*}$  results. The dc-link current reference of the CSI modulator thus becomes

$$i_{\rm dc,CSI,mod}^* = \frac{P^*}{v_{\rm dc,CSI}^*} = \frac{P^*}{v_{\rm CSR}^* - v_{\rm L}^*} > i_{\rm dc,CSI}^*;$$

the CSI operates with 3/3-PWM and controls the dc-link current.

The proposed synergetic control method from **Fig. 8** thus ensures that always one stage operates with 3/3-PWM and controls the dc-link current such that the other stage can operate with 2/3-PWM. As the control structure works with instantaneous (local average) quantities, seamless transitions between operating points are achieved. Further, also the transition region is covered, where the roles of the CSR and the CSI swap multiple times during a fundamental grid or motor period.

Table II

Key components of the realized AC-AC CSC demonstrator from Fig. 10.

| Parameter                                                                                                     |                                                   | Value Unit                                                         |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|

| Switching Frequency                                                                                           | $f_{ m S}$                                        | 72 kHz                                                             |

| dc-link ind.                                                                                                  | 2 x L <sub>dc</sub> /2                            | 2 x 600 μH @ 6 A<br>2 x 00K3515E060<br>3 stacked, 54 turns         |

| EMI 1 <sup>st</sup> st. CM ind.                                                                               | $L_{ m cm1}$                                      | 4 mH @ 72 kHz<br>VAC 500F 30x20x10,<br>2 stacked, 10 turns         |

| EMI 1 <sup>st</sup> st. CM cap.                                                                               | $C_{ m cm1}$                                      | 0.1 μF                                                             |

| EMI 1 <sup>st</sup> st. DM ind.<br>EMI 1 <sup>st</sup> st. CSR DM cap.<br>EMI 1 <sup>st</sup> st. CSI DM cap. | $L_{ m dm1},L_{ m DM1} \ C_{ m dm1} \ C_{ m DM1}$ | 220 μH<br>3.6 μF<br>3.26 μF                                        |

| EMI 2 <sup>nd</sup> st. CM ind. EMI 2 <sup>nd</sup> st. CM cap.                                               | $L_{ m cm2},L_{ m CM2}$ $C_{ m cm2},C_{ m CM2}$   | 2 x 1.1 mH @ 72 kHz<br>2 x VAC 500F,<br>16x10x06, 9 turns<br>10 nF |

| EMI 2 <sup>nd</sup> st. DM ind.<br>EMI 2 <sup>nd</sup> st. CSR DM cap.<br>EMI 2 <sup>nd</sup> st. CSI DM cap. | $L_{ m dm2},L_{ m DM2}$ $C_{ m dm2}$ $C_{ m DM2}$ | 33 μH<br>1.8 μF<br>2.2 μF                                          |

#### IV. EXPERIMENTAL VERIFICATION

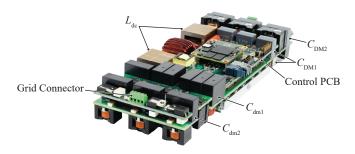

The proposed synergetic control method and the expected improvement of the system efficiency compared to conventional operation is experimentally verified with the ac-ac CSC hardware demonstrator shown in **Fig. 10** with specifications given in **Tab. I** and key component values listed in **Tab. II**. The demonstrator consists of two PCBs, a control and measurement PCB carrying a Xilinx Zynq 7000 SoC, and a power PCB with the CSR and CSI commutation cells based on first-generation 600 V, 140 m $\Omega$  GaN M-BDSs. Further details about the design of the hardware have been presented by the authors in [41] and are not reiterated here for the sake of brevity. All tests have been carried out with resistive load instead of a motor with the load resistor value manually adjusted to obtain desired output voltage for a given current reference.

#### A. Steady-State and Transient Waveforms

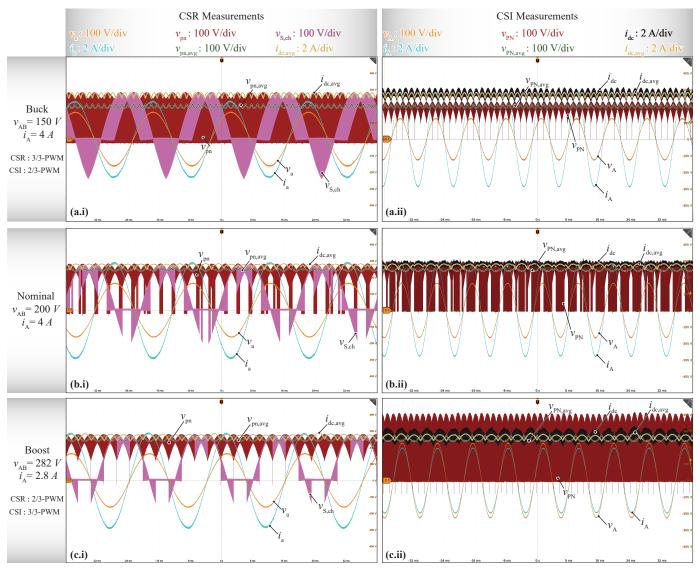

**Fig. 11** shows measured key waveforms for buck operation with  $V_{\rm m} < V_{\rm g}$  in **Fig. 11a**, for nominal operation with  $V_{\rm m} = V_{\rm g}$  in **Fig. 11b**, and for boost operation with  $V_{\rm m} > V_{\rm g}$  in **Fig. 11c**.

1) Buck Mode: In buck mode, the the dc-link current  $i_{\rm dc}$  equals the absolute maximum of the load-side phase currents according to (7) and hence the CSI operates with 2/3-PWM; the absence of zero states is evident in the  $v_{\rm PN}$  waveform in **Fig. 11a.ii**, which toggles only between line-to-line voltages but does not attain zero. Note further that the local average value of the dc-link current,  $i_{\rm dc,avg}$ , superimposed on the CSR measurements in **Fig. 11a.i** is always higher than the amplitude of the grid currents. Therefore, the CSR modulator must use both, active and zero states, which results in  $v_{\rm pn}$  toggling between line-to-line voltages and zero in every switching period.

<sup>9</sup>Note that as a starting step,  $v_L^*$  could also be subtracted from  $v_{CSR}^*$  to form a virtual dc-side voltage reference of the CSI,  $v_{CSI}^{**} = v_{CSR}^* - v_L^*$ , instead, which would then result in a different but functionally equivalent derivation of the final dc-link current references  $i_{dc,CSR,mod}$  and  $i_{dc,CSL,mod}$ .

Fig. 9. Power circuit of the realized 200 V (line-to-line rms), 1.4 kW ac-ac CSC demonstrator using first-generation 600 V, 140 m $\Omega$  GaN M-BDSs, the corresponding hardware prototype is shown in Fig. 10.

**Fig. 10.** Top view of the demonstrator prototype for the circuit of **Fig. 9**. The dimensions of 92 mm x 247 mm x 35 mm result in a power density of 1.8 kW/dm<sup>3</sup> (30 W/in<sup>3</sup>) including the EMI filters on both, grid and motor side, which are designed for compliance with CISPR 11 Class A for 150 kHz–30 MHz and the upcoming IEC TS 62578 C2 for 9 kHz–150 kHz. **Tab. II** summarizes the key components used.

Note that  $S_{ch}$  switches both, positive and negative voltages during the grid period. Additionally, it is interesting to observe that since the dc-link current reference,  $i_{dc}^*$ , is determined from the load phase currents, the measured dc-link current,  $i_{dc}$ , varies with 6 times the load frequency of  $f_m = 110\, Hz$ . Thus, corresponding to constant power flow, the local average values  $v_{pn,avg}$  and  $v_{PN,avg}$  of the switched dc-side voltages of the CSR and the CSI vary with 6  $f_M$ , too, but show an inverted shape such that the  $i_{dc,avg} \cdot v_{pn,avg} = i_{dc,avg} \cdot v_{PN,avg} = P = const$ .

- 2) Transition Mode (Nominal Operating Point): At the nominal operating point ( $V_{\rm g,n}=200\,{\rm V},V_{\rm m,n}=200\,{\rm V}$  and  $P_{\rm n}=1.4\,{\rm kW}$ , see Fig. 2), operation with different grid and load frequencies results in the instantaneous value of  $i_{\rm dc}^*$  being alternatingly defined by the CSR or the CSI, which is clearly visible in particular in the local average waveforms  $i_{\rm dc,avg}, v_{\rm pn,avg}$ , and  $v_{\rm PN,avg}$  in Fig. 11b. Thus, the system operates in the transition mode, and at any point in time, one of the two stages employs 2/3-PWM while the other stage uses 3/3-PWM. This is clearly visible from the switched dc-side voltages  $v_{\rm pn}$  and  $v_{\rm PN}$ , which show mutually exclusive intervals during which the zero level (corresponding to the zero vector) is continuously avoided.

- 3) Boost Mode: In boost mode, the roles of the CSR and the CSI reverse compared to buck mode, i.e., the CSR operates with 2/3-PWM while the CSI uses 3/3-PWM. The dc-link current reference  $i_{\rm dc}^*$  is now defined by the grid currents and therefore the local average value  $i_{\rm dc,avg}$  follows the grid phase currents and, like  $v_{\rm pn,avg}$  and  $v_{\rm PN,avg}$ , shows a fluctuation at

$6f_{\rm g}$ . The CSR's dc-side voltage  $v_{\rm pn}$  now switches between line-to-line voltages while the CSI's dc-side voltage  $v_{PN}$  also attains zero. This is further confirmed by the measured voltage across the M-BDS Sch (high-side commutation cell, phase c) of the CSR,  $v_{S,ch}$ :  $v_{S,ch}$  is only HF-switching during half of the entire grid period (actively taking part in commutations for only one-third of the grid period where  $v_{S,ch}$  switches between zero and a line-to-line voltage and passively for one-sixth of the grid period where  $v_{S,ch}$  switches between two line-to-line voltages, the voltage across it is changed passively due to the commutations between the commutation cell's other two M-BDSs). For the remaining time period, Sch is clamped either in the on-state ( $v_{S,ch} = 0 \text{ V}$ ) or in the off-state, where one of the other two M-BDSs of the commutation cell is clamped to on-state; in particular in the regions that correspond to the highest switched voltages with 3/3-PWM as seen from  $v_{S,ch}$ during buck operation of **Fig. 11.a.i** where  $v_{S,ch}$  HF-switches throughout the entire grid period (actively taking part in the commutations for two third of the period and passively for the remaining one third of the time).

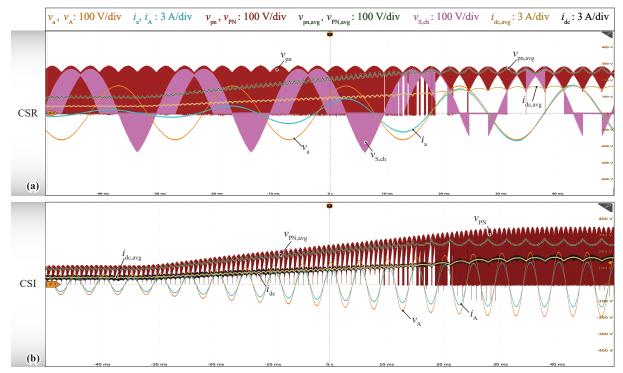

4) Mode Transitions: The proposed synergetic control of the ac-ac CSC is also verified experimentally with varying output voltages  $V_{\rm m}$  as shown in **Fig. 12**. Since the measurements were performed with a fixed resistive load of  $50\,\Omega$ , increasing the output current reference from 1 A to 3 A also leads to a proportional increase of  $V_{\rm m}$ . As can be seen in **Fig. 12**, the proposed control structure ensures a seamless transition from buck to boost mode while ensuring that at any point in time either the CSI or the CSR operate with 2/3-PWM.

#### B. Efficiency Measurement

To quantify the efficiency improvement achieved with synergetic operation compared to conventional operation of the ac-ac CSC throughout the operating area from **Fig. 2**, the efficiency of the hardware demonstrator supplying a resistive load from a mains with  $V_{\rm g,n}=200\,\rm V$  has been measured with a power analyzer (Yokogawa WT1800) and **Fig. 13** summarizes the results. Specifically, **Fig. 13a,d** show the efficiency  $\eta_{\rm ac-ac,conv}$  and the overall losses  $P_{\rm loss,ac-ac,conv}$  for conventional operation, and **Fig. 13b,e** likewise show  $\eta_{\rm ac-ac,syn}$  and  $P_{\rm loss,ac-ac,syn}$  for loss-optimal operation with synergetic control. The color inside of the indicated circles represent measured values whereas the colored contour surfaces in

**Fig. 11.** Measured key waveforms of the ac-ac CSC demonstrator from **Fig. 10** operating with the proposed synergetic control,  $V_{g,n} = 200 \,\text{V}$ ,  $f_g = 50 \,\text{Hz}$ ,  $f_m = 110 \,\text{Hz}$ , three different output voltages  $V_m$  and resistive load; **(a.i)**, **(b.i)**, **(c.i)** CSR and **(a.ii)**, **(b.ii)**, **(c.ii)** CSI. For both stages, one phase voltage, one phase current, and the switched dc-side voltage are shown. Further,  $v_{S,ch}$  is the voltage measured across the M-BDS of phase c in the CSR's high-side commutation cell, and  $i_{dc}$  is the measured dc-link current. The local average values of the switched dc-side voltages of the CSR and the CSI,  $v_{pn,avg}$  and  $v_{PN,avg}$ , as well as of the dc-link current,  $i_{dc,avg}$ , have been calculated from the measured data and superimposed on the oscilloscope screenshots. **(a)** In buck mode,  $i_{dc}$  is defined by the CSI, which thus operates with 2/3-PWM ( $v_{PN}$  does not attain zero) while the CSR operates with 3/3-PWM ( $v_{PN}$  does attain zero), whereas in **(c)** boost mode, the roles of the stages are swapped (note here, too, how  $v_{S,ch}$  remains zero for certain intervals, which corresponds to clamping of  $S_{ch}$ ); **(b)** transition mode, the dc-link reference is alternatingly defined by the CSI, such that both stages alternatingly operate with 2/3-PWM and with 3/3-PWM.

the background are calculation results. <sup>10</sup> The similarity of the colors inside of the circles compared to the surrounding background thus indicates a generally excellent matching between calculation and measurements across the entire operating range for both, conventional and synergetic control. Finally, based on the calculated results, **Fig. 13c** shows the percentage-point gain in overall system efficiency,  $\Delta\eta_{\rm ac-ac} = \eta_{\rm ac-ac,syn} - \eta_{\rm ac-ac,conv}$ , and **Fig. 13f** shows the relative change in losses,  $\Delta p_{\rm loss,ac-ac} = (P_{\rm loss,ac-ac,syn} - P_{\rm loss,ac-ac,conv}) / P_{\rm loss,ac-ac,conv}$ . An improvement in efficiency of 0.3% at nominal operating

<sup>10</sup>The transistor losses are obtained as discussed in **Section II**, the losses of magnetic components are calculated according to [55] and the auxiliary losses, accounting for the power requirements of the gate drives, controller, measurement circuitry and cooling fan are estimated based on similar systems.

point and over 1% at part load operation is measured. This corresponds to a reduction of the overall losses by around 10% at the nominal operating point. Note that the loss reduction / efficiency improvement achieved with the proposed synergetic control would be higher for designs with M-BDSs of lower  $R_{\rm ds,on}$  (and hence larger chip area and higher switching losses), and/or higher switching frequency.

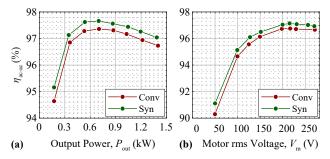

Further, **Fig. 14a** shows the measured efficiency curves of the ac-ac CSC operating with synergetic control and conventional control for a fixed nominal load voltage  $V_{\rm m,n}=200\,\rm V$  while varying the output current and hence, output power. **Fig. 14b** shows the efficiency curves for varying output voltage while limiting the output current according to the maximum power limit, i.e., the thick black boundary line in **Fig. 13**). Again,

Fig. 12. Measured key waveforms of the ac-ac CSC demonstrator from Fig. 10 operating with the proposed synergetic control with  $f_g = 50$  Hz and  $f_m = 200$  Hz. The CSC operates with an input voltage of  $V_{g,n} = 200$  V and supplies a three-phase resistive load of  $50\,\Omega$ , whereby the load current reference is gradually increased from 1 A corresponding to  $V_m = 85$  V (buck mode; the CSR operates with 3/3-PWM and the CSI with 2/3-PWM) to 3 A corresponding to  $V_m = 260$  V (boost mode; the CSR operates with 2/3-PWM and the CSI with 3/3-PWM). Clearly, a seamless transition is achieved, and at any point in time, either the CSR or the CSI operates with 2/3-PWM, which is highlighted by the absence of zero states in the respective dc-side switched voltages  $v_{pn}$  or  $v_{PN}$ . Note further the change in frequency of the local average values  $v_{pn,avg}$ ,  $v_{PN,avg}$  and  $i_{dc,avg}$  from  $6f_m = 1200$  Hz in buck mode to  $6f_g = 300$  Hz in boost mode.

clear efficiency improvements are observed.

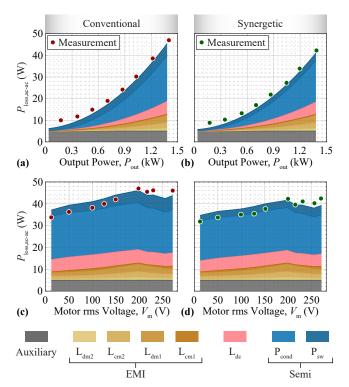

Finally, Fig. 15a,c show the calculated loss breakdowns of the ac-ac CSC, as well as measured losses for operation with conventional control and Fig. 15b,d shows the same for synergetic control; again once for a fixed nominal load voltage  $V_{\rm m,n} = 200 \, \rm V$  and varying output power, and once with varying output voltage while limiting the output current according to the maximum power limit, i.e., the thick black boundary line in Fig. 13). Again, a very good match between calculated and measured system losses is confirmed. Fig. 15 further indicates that semiconductor losses account for the largest share of the total system losses. Within the semiconductor losses, the dominating contributor are the conduction loss  $P_{cond}$  since the available first-generation M-BDSs used for the realization of the ac-ac CSC demonstrator have a comparably high onstate resistance of  $R_{\rm ds,on} = 140 \,\rm m\Omega$ . Note that because  $P_{\rm cond}$ increases with the square of  $i_{dc}$ , the peak efficiency in Fig. 14a is achieved at relatively lower power. On the other hand,  $P_{\text{cond}}$ does not change when varying the output voltage while keeping the maximum possible output power as in Fig. 15c,d. Since synergetic operation ensures 2/3-PWM of one of the two stages for all operating points, the switching losses  $P_{\rm sw}$  in Fig. 15b,d (synergetic control) are clearly lower compared to Fig. 15a,c (conventional control).

#### V. Conclusion

For variable speed drives (VSDs), ac-ac current-source converters (CSCs) are an interesting alternative to ubiquitously

employed ac-ac voltage-source converters (VSCs), because CSCs inherently provide smooth sinusoidal motor voltages with a single magnetic component, i.e., the dc-link inductor that connects the grid-side current-source rectifier (CSR) and the motor-side current-source inverter (CSI).

To maximize the ac-ac conversion efficiency, this paper first describes loss-optimal operation over the full output voltage range: for any operating point, the minimum necessary dc-link current is used, which is defined by the maximum absolute value of any of the six phase currents (three on the grid side, three on the motor side). Therefore, using a corresponding timevarying dc-link current, conduction losses of the transistors and also of the dc-link inductor are minimized. Further, if the dc-link current is defined by the CSI (motor currents higher than the grid currents; buck mode), advantageously one of the CSI's phase currents directly corresponds to the dc-link current. That phase is thus permanently connected to the dc-link inductor (clamped) and only two out of three phase currents are synthesized using pulse-width modulation (PWM), i.e., 2/3-PWM of the CSI is achieved, which minimizes the switching losses. As the dc-link current is always higher than the CSR stage's phase currents, the CSR stage, on the other hand, must use PWM for forming all three phase currents (3/3-PWM), and it can thus be used to shape the dc-link current as needed for 2/3-PWM operation of the CSI stage. Conversely, if the dc-link current is defined by the CSR (motor currents lower than the grid currents; boost mode), the roles of the two stages are exchanged. To quantify the loss reduction compared to